# USER MANUAL

ADRASTEA-I

2615011136000

VERSION 1.8

JANUARY 20, 2026

WÜRTH ELEKTRONIK MORE THAN YOU EXPECT

\*\*\*\*\*

## **MUST READ**

### **Check for firmware updates**

Before using the product, make sure you use the most recent firmware version, data sheet, and user manual. This is especially important for Wireless Connectivity products that were not purchased directly from Würth Elektronik eiSos. A firmware update on these respective products may be required.

We strongly recommend including the possibility of a firmware update in the customer system design.

### **Certification Information:**

The certification information is mandatory to check, see chapter 3.3

### **Power Saving Features:**

The power saving features information is important to check before enabling 3GPP defined eDRX and PSM features, see chapter 7.2, chapter 7.3, chapter 7.4

### **Application MCU:**

Effective January 1, 2026, Sony will discontinue support for Open MCU for all new designs based on the ALT1250 chipset. As a result, using the integrated Arm Cortex M4 MCU of Adrastea-I for new application development is not recommended.

However, using Adrastea-I as a modem is not affected by this announcement.

## Contents

|                                                             |           |

|-------------------------------------------------------------|-----------|

| <b>1 Revision history</b>                                   | <b>5</b>  |

| <b>2 Abbreviations</b>                                      | <b>9</b>  |

| <b>3 Introduction</b>                                       | <b>11</b> |

| 3.1 Adrastea-I GCF Certification . . . . .                  | 12        |

| 3.2 Adrastea-I Deutsche Telekom Certification . . . . .     | 13        |

| 3.3 Benefits of Deutsche Telekom Certified Module . . . . . | 14        |

| 3.4 Module Key Features . . . . .                           | 16        |

| 3.5 Block diagram . . . . .                                 | 17        |

| 3.6 Ordering information . . . . .                          | 17        |

| <b>4 Electrical and Radio Specifications</b>                | <b>18</b> |

| 4.1 Operating Conditions . . . . .                          | 18        |

| 4.2 Current Consumption . . . . .                           | 18        |

| 4.2.1 LTE-Cat.M Mode . . . . .                              | 18        |

| 4.2.2 LTE-Cat.NB-IoT Mode . . . . .                         | 19        |

| 4.3 LTE Radio Characteristics . . . . .                     | 19        |

| 4.3.1 LTE Supported Bands . . . . .                         | 20        |

| 4.3.2 LTE-Cat.M Mode . . . . .                              | 20        |

| 4.3.3 LTE-Cat.NB-IoT Mode . . . . .                         | 20        |

| 4.3.4 RF Receiving Sensitivity . . . . .                    | 21        |

| 4.3.5 LTE-Cat.M Reference sensitivity . . . . .             | 21        |

| 4.3.6 LTE-Cat.NB-IoT Reference sensitivity . . . . .        | 21        |

| 4.3.7 Maximum Output Power . . . . .                        | 22        |

| 4.3.8 LTE-Cat.M Maximum Output Power . . . . .              | 22        |

| 4.3.9 LTE-Cat.NB-IoT Maximum Output Power . . . . .         | 22        |

| 4.4 GNSS Radio Characteristics . . . . .                    | 23        |

| 4.4.1 GNSS Supported Constellation . . . . .                | 23        |

| 4.4.2 GNSS: Operating frequencies . . . . .                 | 23        |

| 4.4.3 GNSS: Rx Sensitivity . . . . .                        | 24        |

| 4.4.4 GNSS: Time To First Fix . . . . .                     | 24        |

| 4.4.5 GNSS: Position Accuracy . . . . .                     | 25        |

| <b>5 Pinout</b>                                             | <b>26</b> |

| 5.1 Module Power Up . . . . .                               | 32        |

| 5.2 Module Power Down . . . . .                             | 34        |

| 5.3 Module Reset . . . . .                                  | 34        |

| 5.4 WAKEUP pin . . . . .                                    | 34        |

| 5.5 AT_IN and AT_OUT pins . . . . .                         | 34        |

| 5.6 /RESET pin . . . . .                                    | 34        |

| 5.7 EXT_ALARM pin . . . . .                                 | 35        |

| 5.8 RF_LTE pin . . . . .                                    | 35        |

| 5.9 RF_GNSS pin . . . . .                                   | 35        |

| 5.10 VBACKUP and VCAP pins . . . . .                        | 35        |

| 5.10.1 VCAP pin . . . . .                                   | 36        |

|          |                                                             |           |

|----------|-------------------------------------------------------------|-----------|

| 5.10.2   | VBACKUP pin . . . . .                                       | 36        |

| 5.10.3   | VDDIO . . . . .                                             | 36        |

| 5.11     | Digital I/O Pins Specifications . . . . .                   | 37        |

| <b>6</b> | <b>Module Interfaces</b>                                    | <b>38</b> |

| 6.1      | UART Interface . . . . .                                    | 38        |

| 6.1.1    | UART Default Configuration . . . . .                        | 38        |

| 6.1.2    | UART0 Pin Interface . . . . .                               | 39        |

| 6.1.3    | UART1 Pin Interface . . . . .                               | 39        |

| 6.1.4    | UART2 Pin Interface . . . . .                               | 40        |

| 6.1.5    | UART0 Host Connection . . . . .                             | 40        |

| 6.2      | SPI Interface . . . . .                                     | 42        |

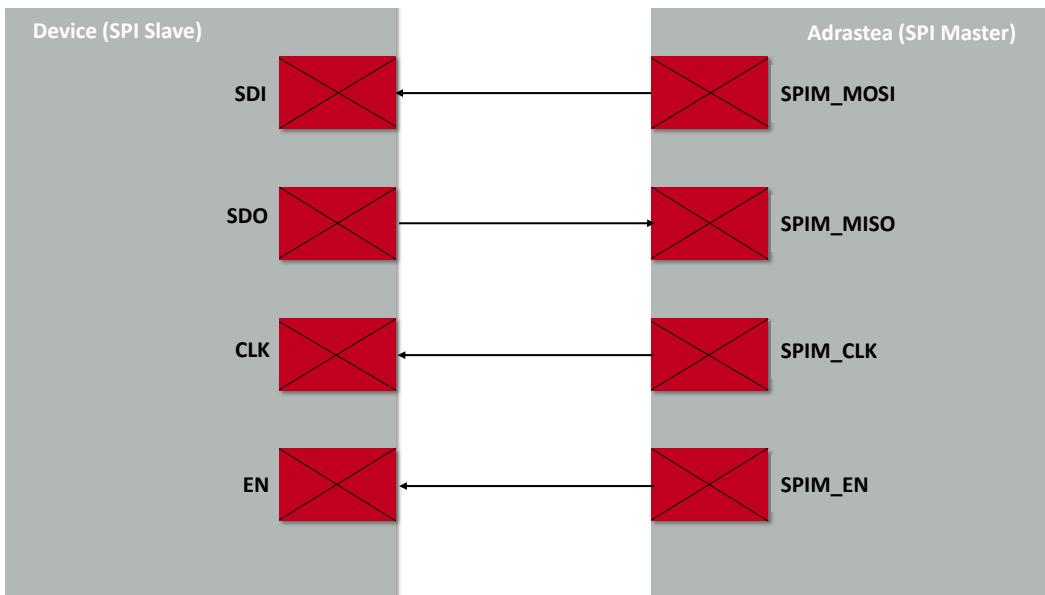

| 6.2.1    | SPIM Pin Interface . . . . .                                | 42        |

| 6.2.2    | SPIM Connection . . . . .                                   | 42        |

| 6.3      | I <sup>2</sup> C Interface . . . . .                        | 44        |

| 6.3.1    | I <sup>2</sup> C Pin Interface . . . . .                    | 44        |

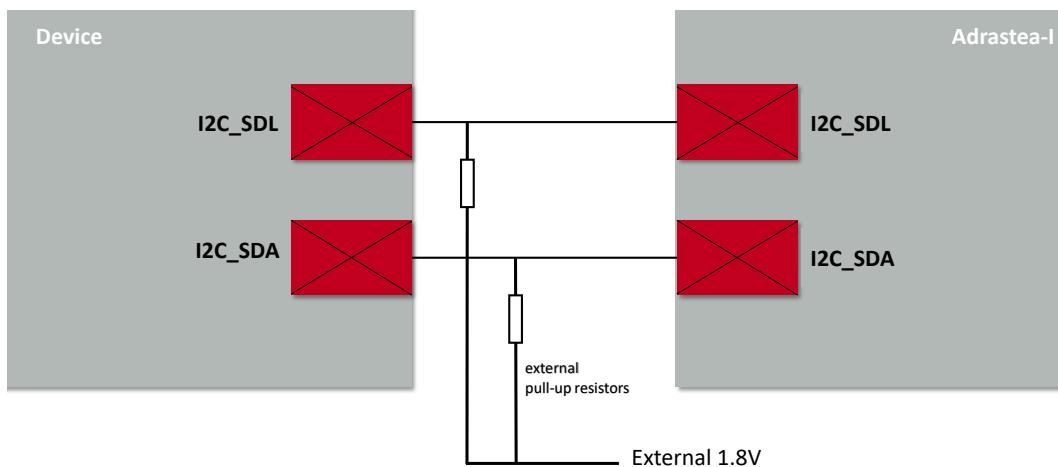

| 6.3.2    | I <sup>2</sup> C Connection . . . . .                       | 44        |

| 6.4      | ADC Interface . . . . .                                     | 46        |

| 6.4.1    | ADC Functional Specifications . . . . .                     | 46        |

| 6.4.2    | ADC Pin Interface . . . . .                                 | 47        |

| 6.5      | SIM Interface . . . . .                                     | 47        |

| 6.5.1    | SIM Pin Interface . . . . .                                 | 47        |

| 6.6      | RF interfaces . . . . .                                     | 48        |

| 6.7      | E-JTAG Debug port . . . . .                                 | 48        |

| 6.8      | GPIO Pin Information . . . . .                              | 49        |

| <b>7</b> | <b>Functional description</b>                               | <b>52</b> |

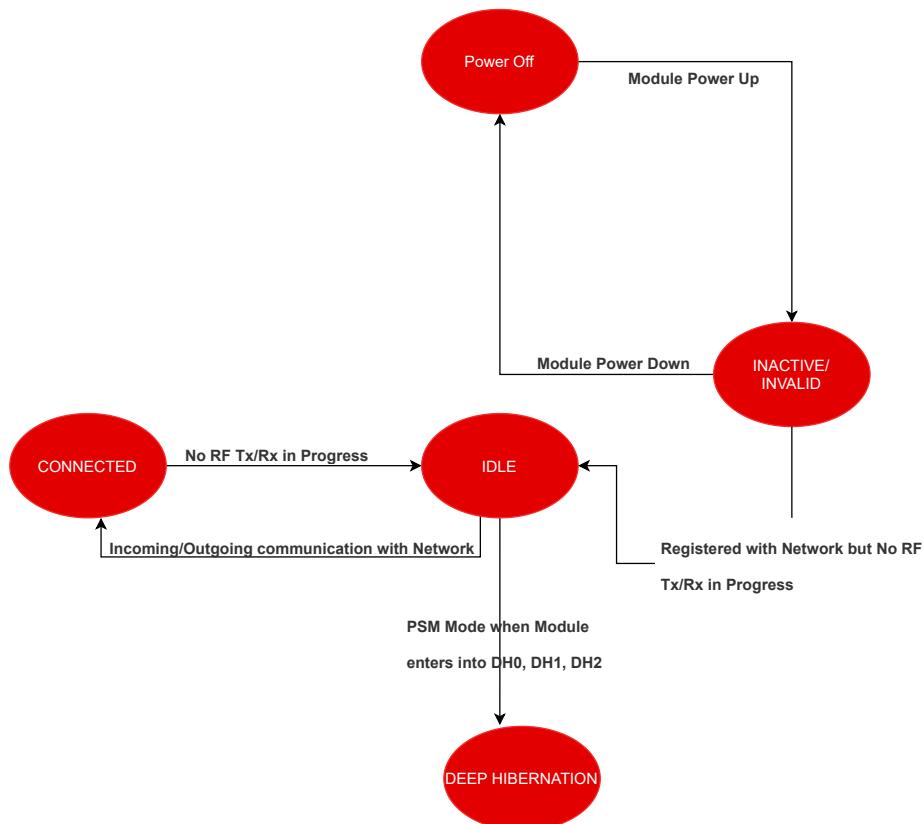

| 7.1      | Adrastea-I State Transition . . . . .                       | 52        |

| 7.2      | Power Saving Features . . . . .                             | 53        |

| 7.3      | Network Operator Support . . . . .                          | 53        |

| 7.4      | Network Independent Adrastea-I Power Saving Modes . . . . . | 53        |

| 7.4.1    | DH0 Mode . . . . .                                          | 53        |

| 7.4.2    | DH1 Mode . . . . .                                          | 54        |

| 7.4.3    | DH2 Mode . . . . .                                          | 54        |

| 7.4.4    | DH0 Mode Setting . . . . .                                  | 55        |

| 7.4.5    | DH1 Mode Setting . . . . .                                  | 56        |

| 7.4.6    | DH2 Mode Setting . . . . .                                  | 58        |

| 7.5      | GNSS Receiver . . . . .                                     | 60        |

| 7.5.1    | Supported GNSS constellations . . . . .                     | 60        |

| 7.5.2    | GNSS Co-existence with LTE Modem . . . . .                  | 60        |

| 7.6      | Application MCU . . . . .                                   | 60        |

| <b>8</b> | <b>Quick start guide</b>                                    | <b>61</b> |

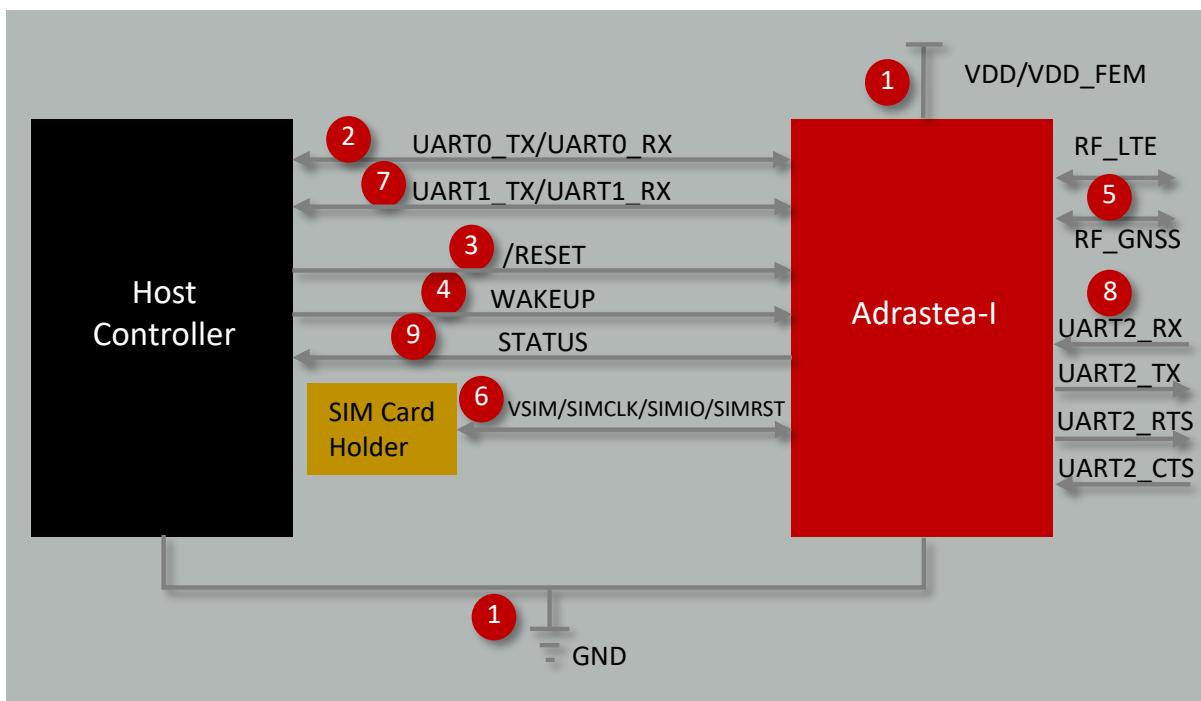

| 8.1      | Minimal pin connections . . . . .                           | 61        |

| 8.2      | Prerequisites . . . . .                                     | 62        |

| 8.3      | Taking into operation . . . . .                             | 64        |

| 8.4      | Select LTE-M or NB-IoT Mode . . . . .                       | 67        |

| 8.4.1    | Manual selection of LTE-M or NB-IoT mode . . . . .          | 67        |

|           |                                                  |           |

|-----------|--------------------------------------------------|-----------|

| 8.4.2     | Automatic Selection of LTE-M or NB-IoT Mode      | 68        |

| 8.5       | Register to Network                              | 70        |

| 8.6       | Activate GNSS                                    | 72        |

| <b>9</b>  | <b>Design in guide</b>                           | <b>74</b> |

| 9.1       | Advice for schematic and layout                  | 74        |

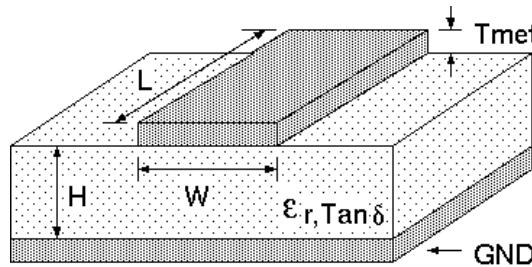

| 9.2       | Dimensioning of the micro strip antenna line     | 76        |

| 9.3       | Antenna solutions                                | 76        |

| 9.3.1     | Wire antenna                                     | 77        |

| 9.3.2     | Chip antenna                                     | 77        |

| 9.3.3     | PCB antenna                                      | 77        |

| 9.3.4     | Antennas provided by Würth Elektronik eiSos      | 77        |

| 9.3.4.1   | 2600130084 - Hati-I - LTE antenna                | 78        |

| <b>10</b> | <b>Reference design</b>                          | <b>79</b> |

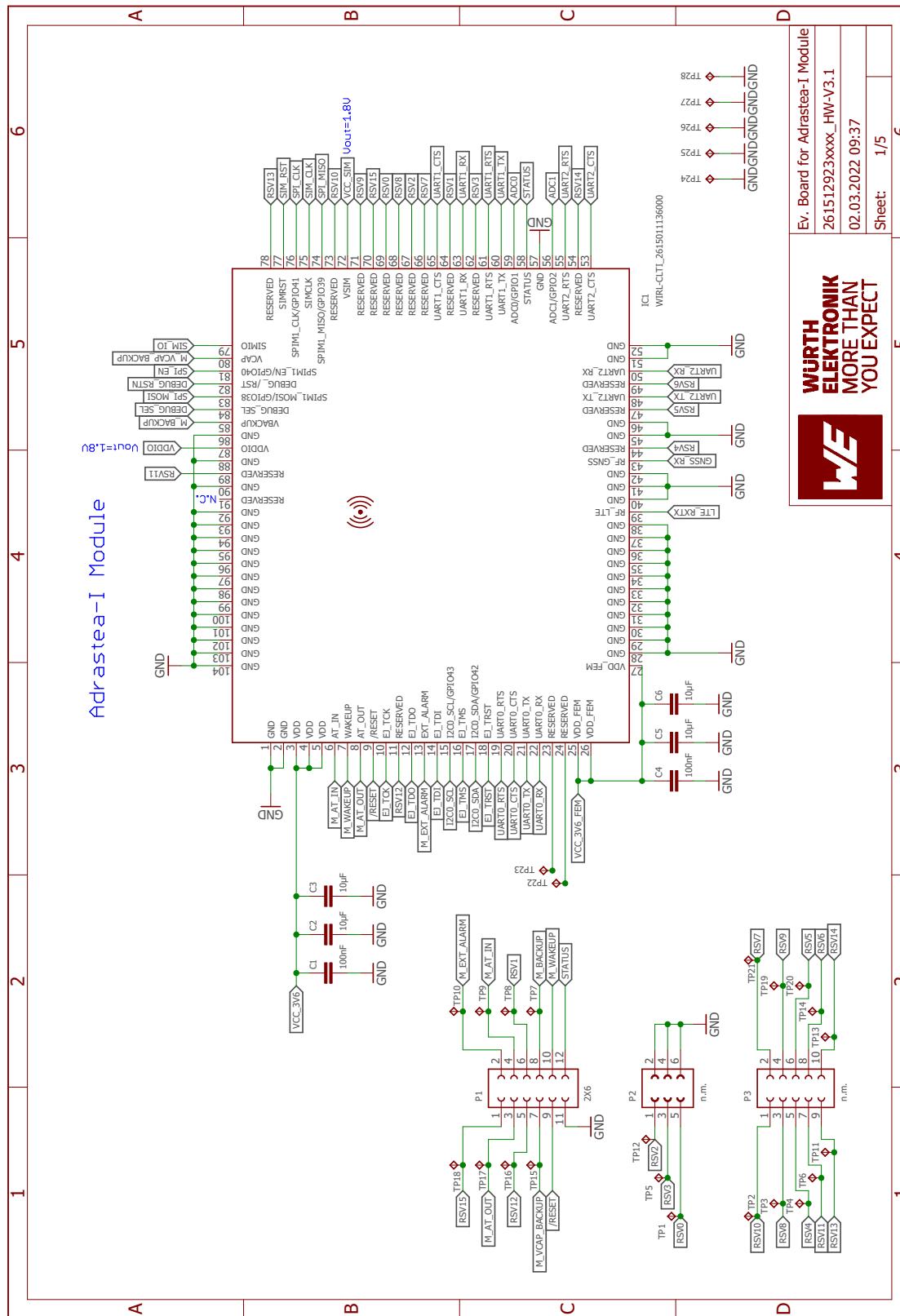

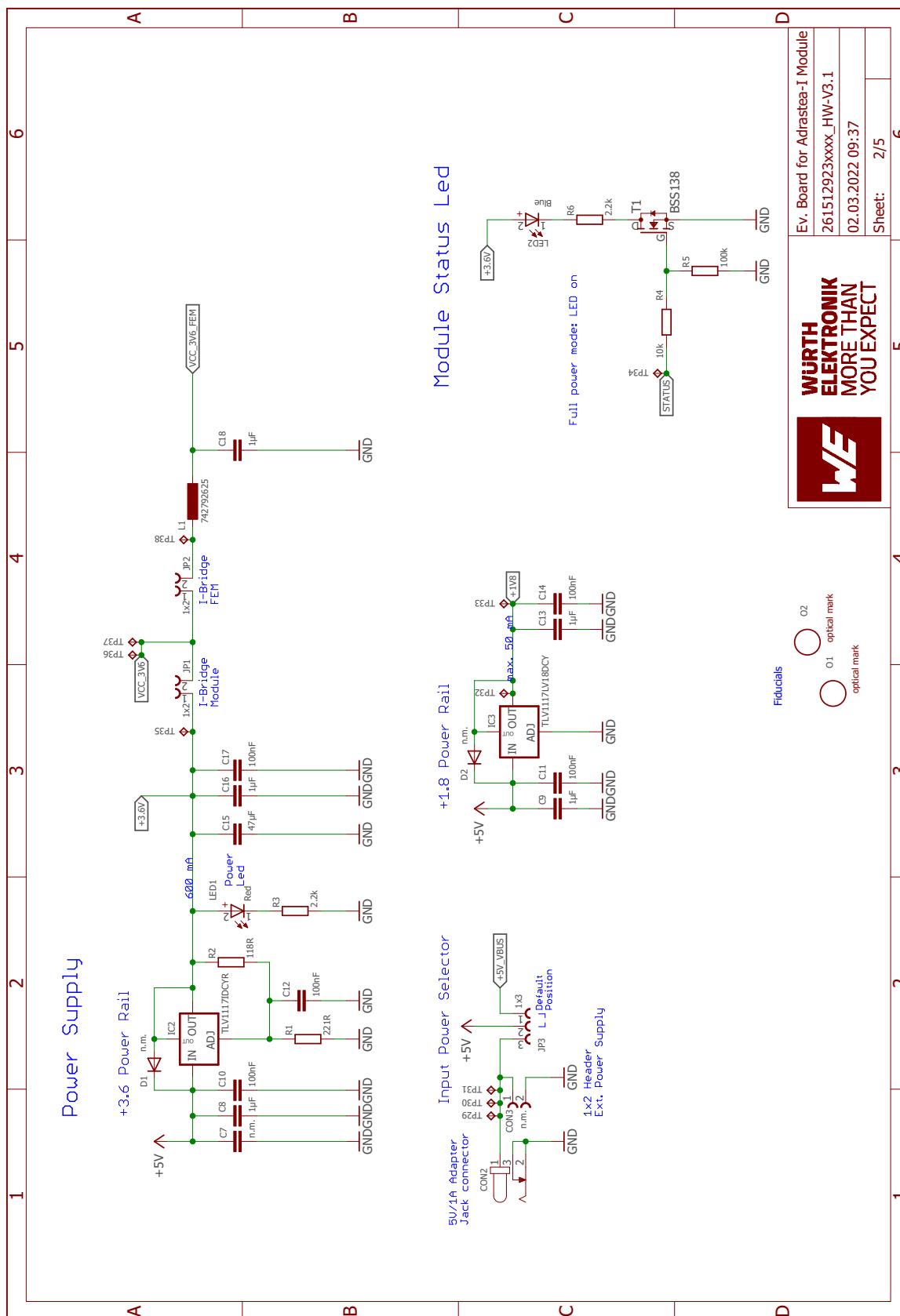

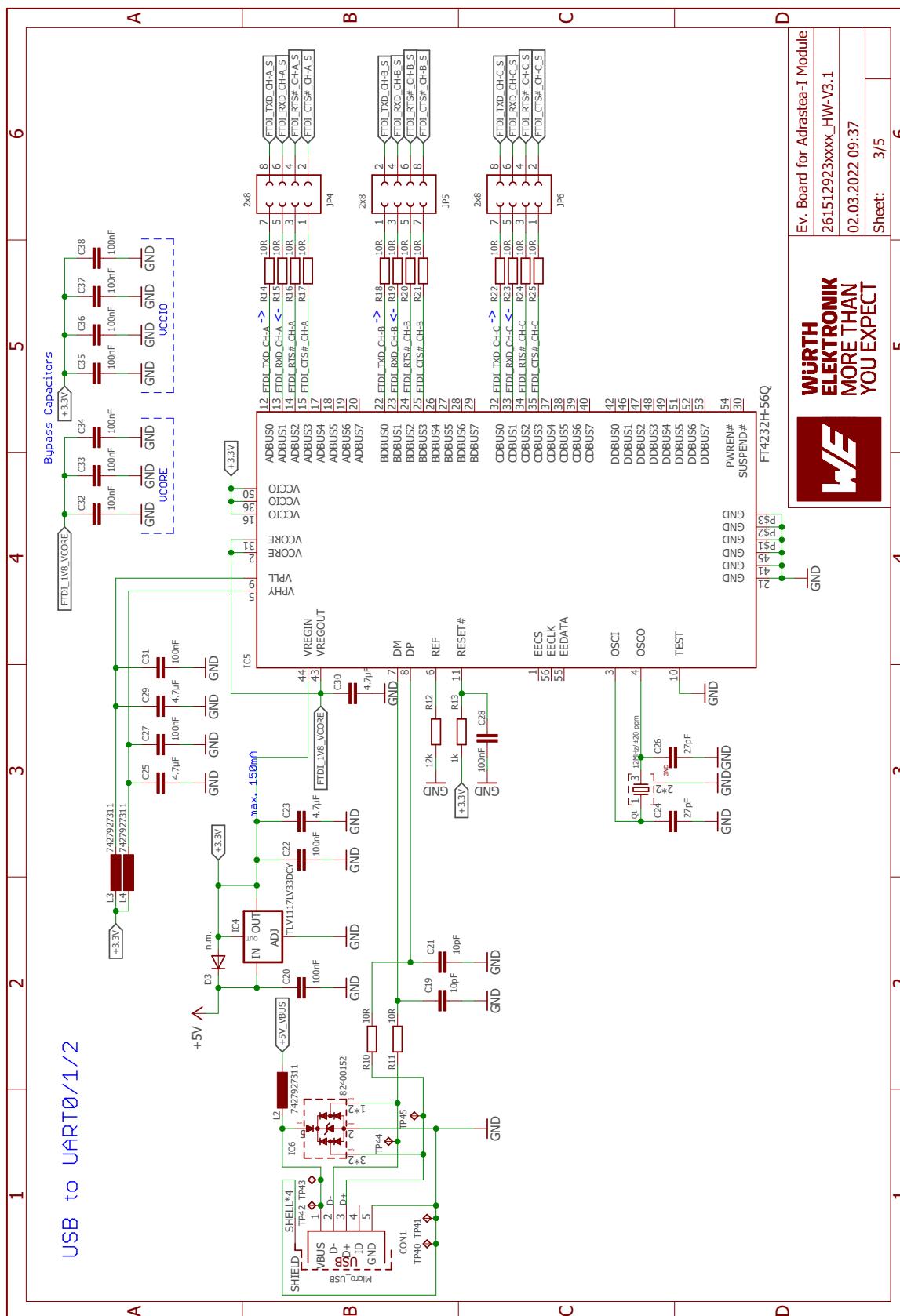

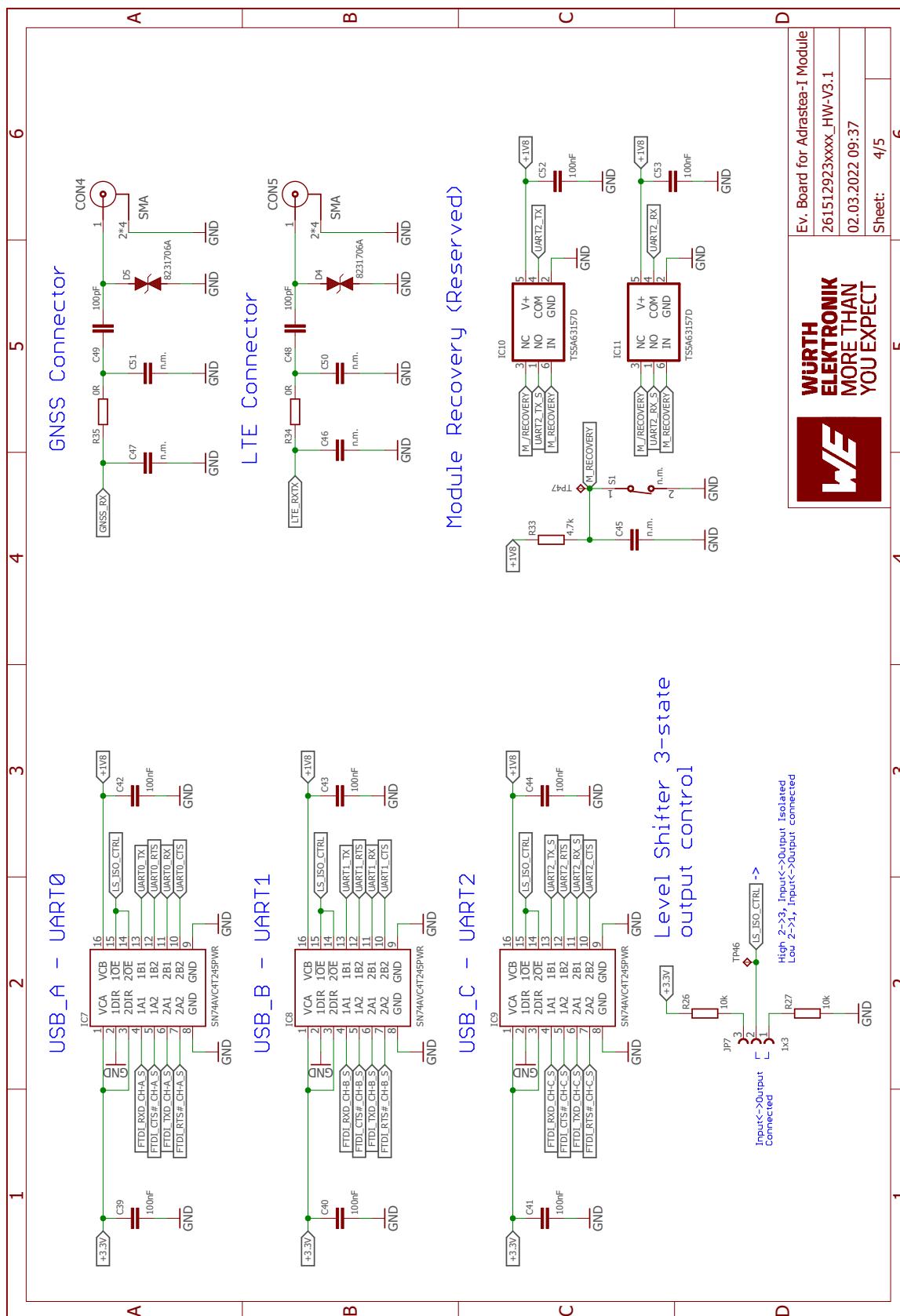

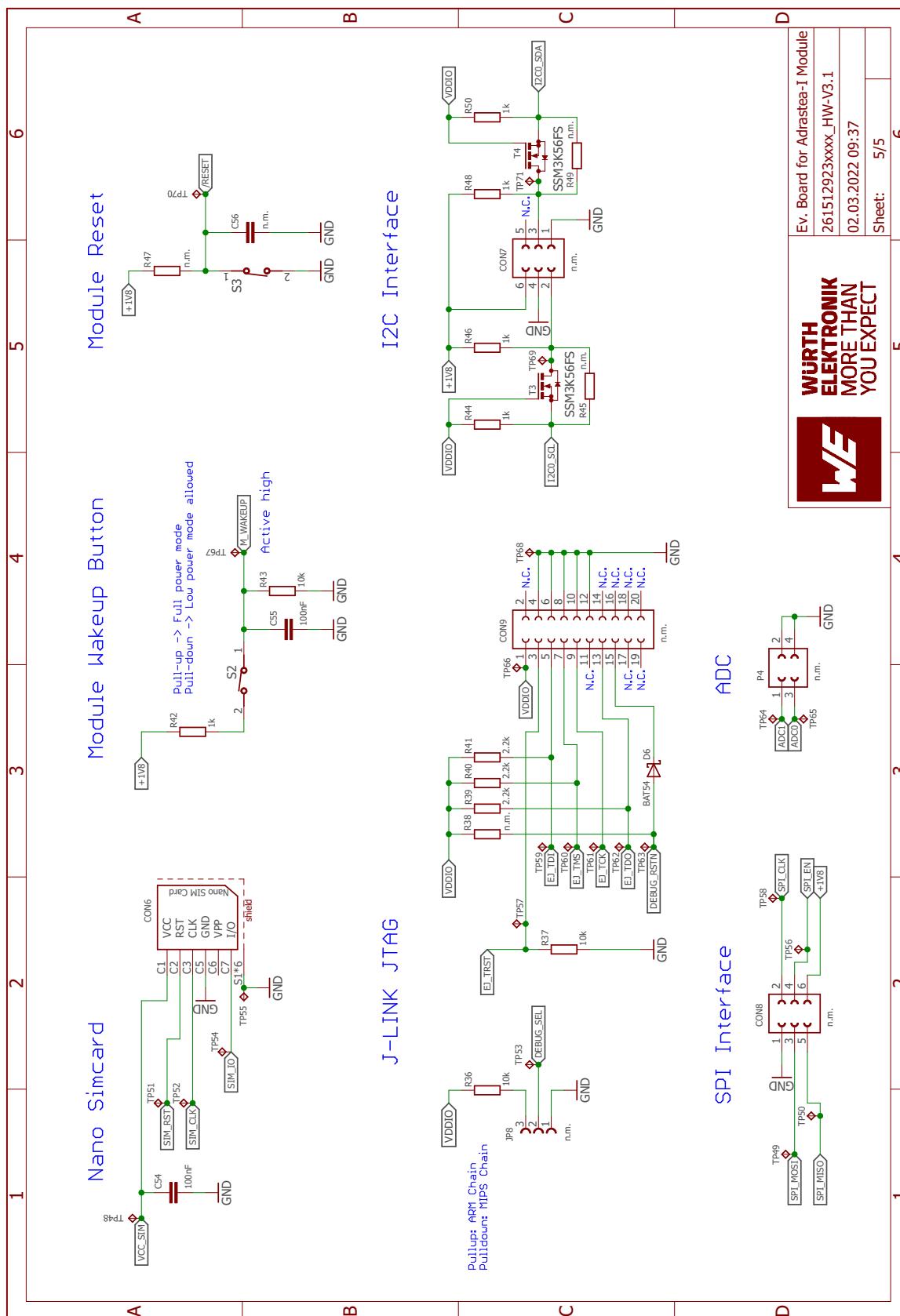

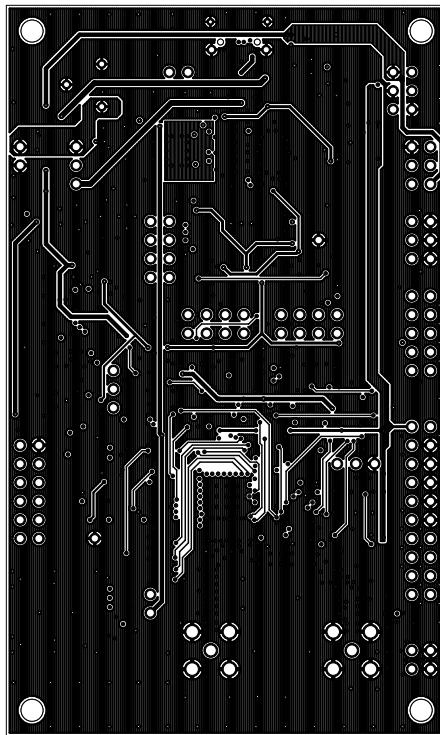

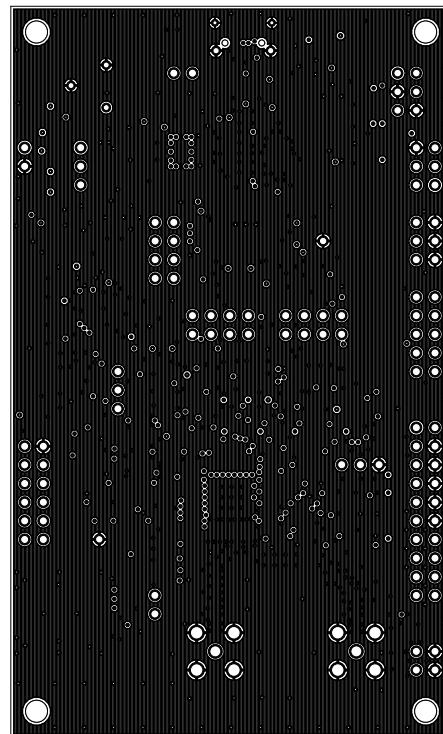

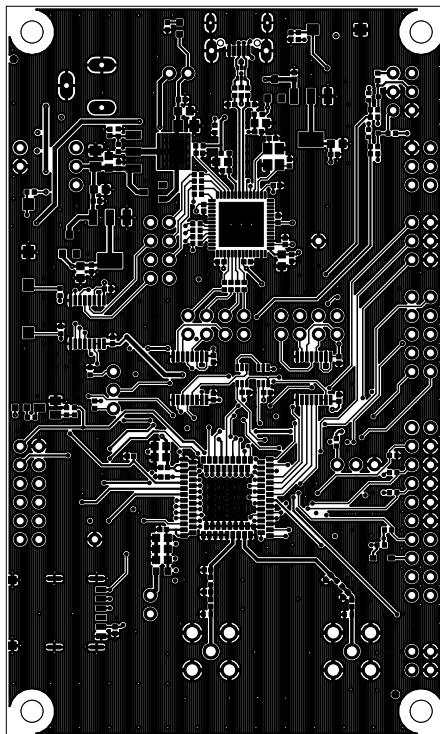

| 10.1      | Schematic                                        | 80        |

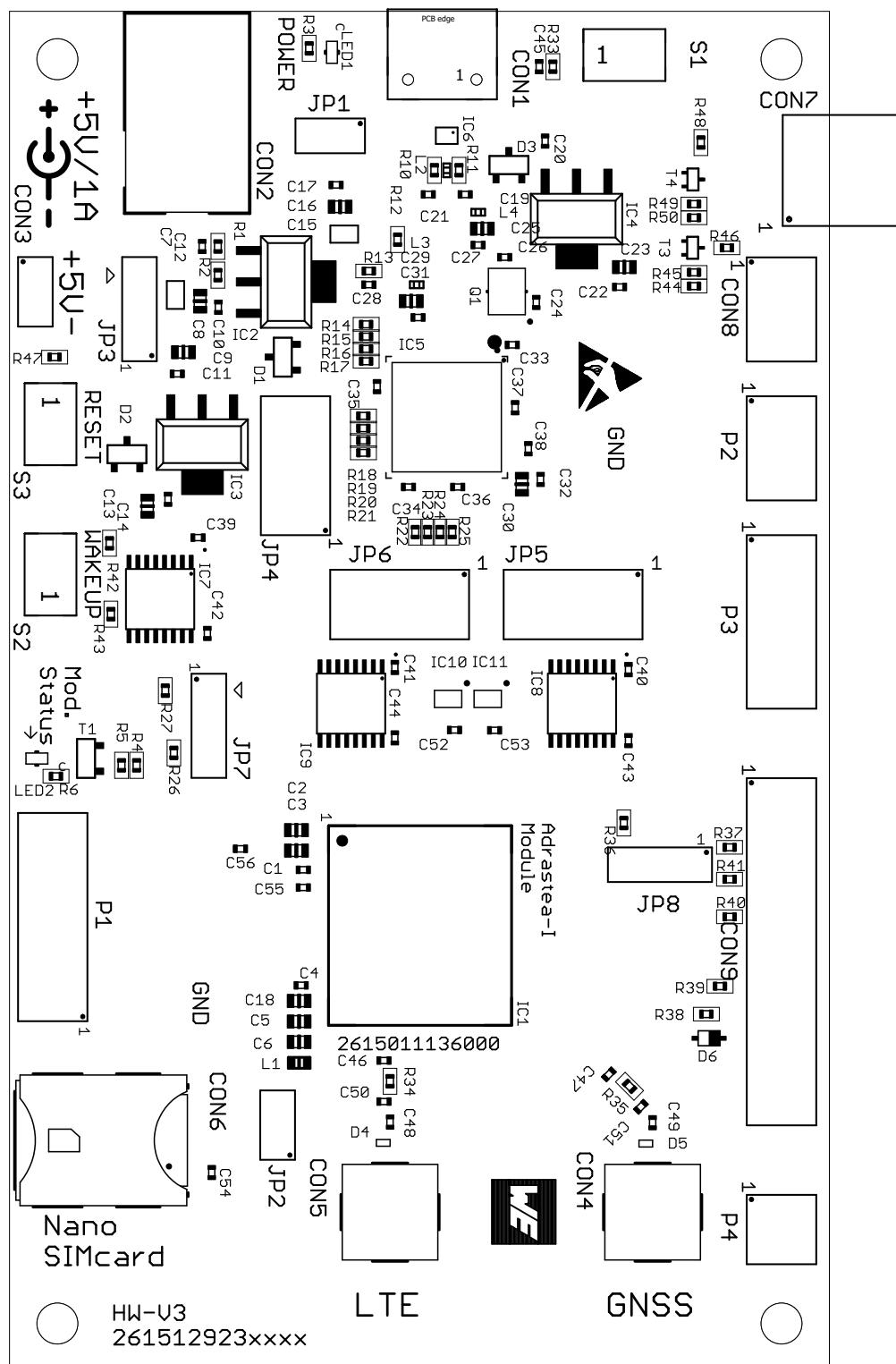

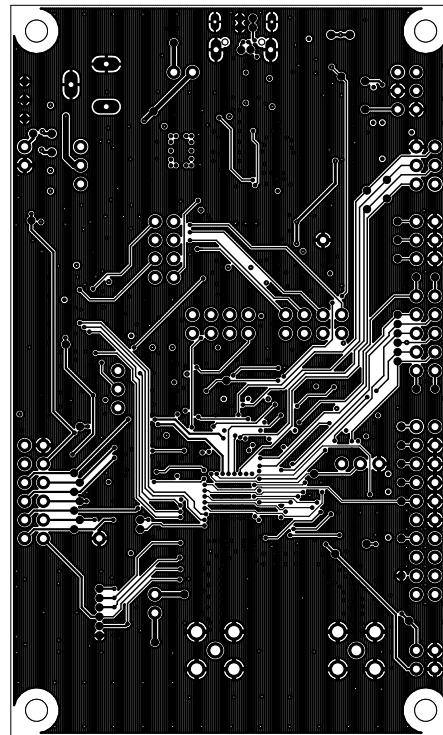

| 10.2      | Layout                                           | 85        |

| <b>11</b> | <b>Manufacturing information</b>                 | <b>87</b> |

| 11.1      | Moisture sensitivity level                       | 87        |

| 11.2      | Soldering                                        | 87        |

| 11.2.1    | Reflow soldering                                 | 87        |

| 11.2.2    | Cleaning                                         | 88        |

| 11.2.3    | Potting and coating                              | 89        |

| 11.2.4    | Other notations                                  | 89        |

| 11.3      | ESD handling                                     | 89        |

| 11.4      | Safety recommendations                           | 90        |

| <b>12</b> | <b>Product testing</b>                           | <b>91</b> |

| 12.1      | Würth Elektronik eiSos in-house production tests | 91        |

| 12.2      | EMS production tests                             | 91        |

| <b>13</b> | <b>Physical specifications</b>                   | <b>93</b> |

| 13.1      | Dimensions                                       | 93        |

| 13.2      | Weight                                           | 93        |

| 13.3      | Module drawing                                   | 94        |

| 13.4      | Footprint                                        | 95        |

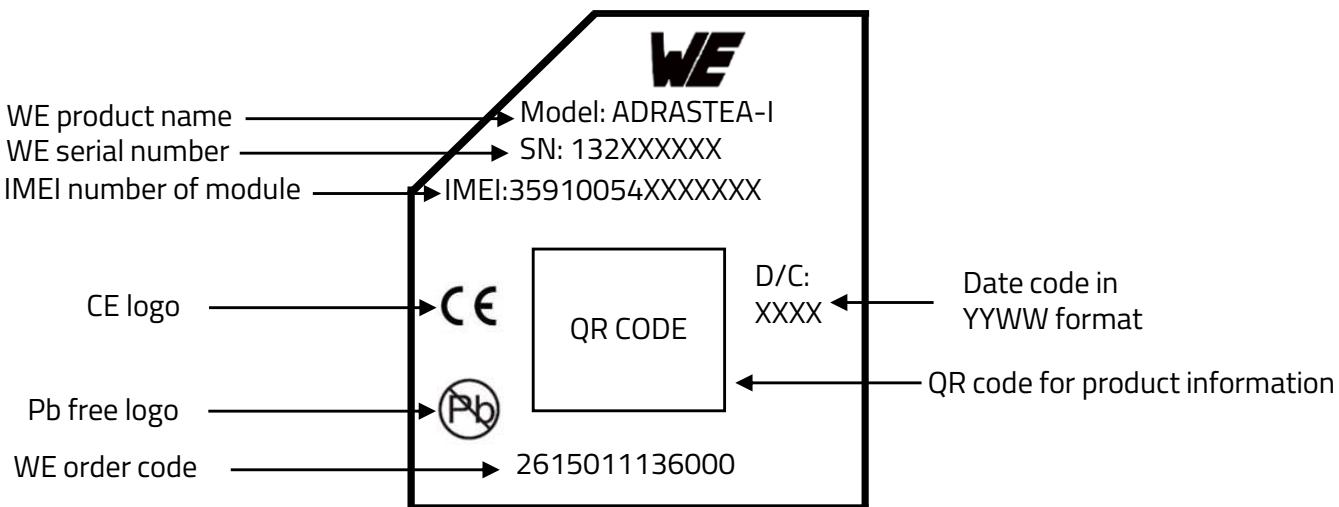

| <b>14</b> | <b>Marking</b>                                   | <b>96</b> |

| 14.1      | Lot number                                       | 96        |

| 14.2      | General labeling information                     | 97        |

| <b>15</b> | <b>Information for explosion protection</b>      | <b>98</b> |

| <b>16</b> | <b>Regulatory compliance information</b>         | <b>99</b> |

| 16.1      | Important notice EU                              | 99        |

| 16.2      | Important notice UKCA                            | 99        |

| 16.3      | Conformity assessment of the final product       | 99        |

| 16.4      | Exemption clause                                 | 99        |

---

|           |                                                                           |            |

|-----------|---------------------------------------------------------------------------|------------|

| 16.5      | EU Declaration of conformity . . . . .                                    | 101        |

| 16.6      | RED-DA Cybersecurity statement . . . . .                                  | 102        |

| 16.7      | RED-DA Cybersecurity first actions . . . . .                              | 103        |

| 16.8      | RED-DA Cybersecurity guideline for end devices using Adrastea-I . . . . . | 106        |

| <b>17</b> | <b>References</b>                                                         | <b>108</b> |

| <b>18</b> | <b>Important notes</b>                                                    | <b>109</b> |

| <b>19</b> | <b>Legal notice</b>                                                       | <b>109</b> |

| <b>20</b> | <b>License terms</b>                                                      | <b>110</b> |

# 1 Revision history

| Manual version         | FW version       | HW version | Notes                                                                                                                                                                                                                                                                                                                                                                                                                                     | Date        |

|------------------------|------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 1.0                    | ADRASTEAI_06.006 | 1.0        | <ul style="list-style-type: none"> <li>Initial release of the manual</li> </ul>                                                                                                                                                                                                                                                                                                                                                           | April 2022  |

| 1.1                    | ADRASTEAI_06.006 | 1.0        | <ul style="list-style-type: none"> <li>Added section Adrastea-I GCF Certification.</li> <li>Added section Minimal pin connections.</li> <li>Updated section Application MCU.</li> </ul>                                                                                                                                                                                                                                                   | May 2023    |

| 1.2                    | ADRASTEAI_06.006 | 1.0        | <ul style="list-style-type: none"> <li>Actualized section Regulatory compliance information.</li> </ul>                                                                                                                                                                                                                                                                                                                                   | August 2023 |

| 1.3                    | ADRASTEAI_06.006 | 1.0        | <ul style="list-style-type: none"> <li>Updated information about GNSS update rate in section GNSS: Time To First Fix.</li> <li>Updated GPIO Pin Information in section GPIO Pin Information.</li> <li>Redundant sections 3.11 and 3.12 removed. Content can be found in section GPIO Pin Information and E-JTAG Debug port.</li> <li>Updated information about bootdelay configurations in section UART Default Configuration.</li> </ul> | August 2024 |

| Continued on next page |                  |            |                                                                                                                                                                                                                                                                                                                                                                                                                                           |             |

|     |                  |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |              |

|-----|------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| 1.3 | ADRASTEAI_06.006 | 1.0 | <ul style="list-style-type: none"> <li>Added new section DH0 Mode Setting.</li> <li>Added new section DH1 Mode Setting.</li> <li>Added new section DH2 Mode Setting.</li> <li>Updated link for Sony MCU access request in section Application MCU.</li> <li>Updated section Select LTE-M or NB-IoT Mode.</li> <li>Updated figure with more dimentions in section Footprint.</li> <li>Added information about LTE antenna in section Antenna solutions.</li> <li>Updated General labelling information for Adrastea-I in section General labeling information.</li> <li>Added Information for explosion protection for Adrastea-I in section Information for explosion protection.</li> <li>Abbreviations section updated.</li> </ul> | August 2024  |

| 1.4 | ADRASTEAI_06.006 | 1.0 | <ul style="list-style-type: none"> <li>Added chapter Product testing</li> <li>Added chapter Important notice UKCA</li> <li>Removed chapter "LOT number"</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | October 2024 |

|     |                  |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |            |

|-----|------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 1.5 | ADRASTEAI_06.006 | 1.0 | <ul style="list-style-type: none"> <li>Removed iotcreator connectivity information</li> <li>Updated information in section Benefits of Deutsche Telekom Certified Module</li> <li>Updated information in Chapter Pinout</li> <li>Updated information in Chapter GPIO Pin Information</li> <li>Updated information in Chapter Functional description</li> <li>Added Lot number information Chapter Lot number</li> </ul>                                                                                       | April 2025 |

| 1.6 | ADRASTEAI_06.006 | 1.0 | <ul style="list-style-type: none"> <li>Added EN 301 489-52 to Regulatory compliance information.</li> <li>Added TLS Version information to Module Key Features.</li> <li>Updated Minimal pin connections picture with SIM card holder to Minimal pin connections.</li> <li>Updated SIM information in to Minimal pin connections.</li> <li>Added extra step to check internet connection in to Register to Network.</li> <li>Added information about ISO 7816 information in to SIM Pin Interface.</li> </ul> | July 2025  |

|     |                       |     |                                                                                                                                                           |              |

|-----|-----------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| 1.7 | ADRASTEAL<br>I_06.006 | 1.0 | <ul style="list-style-type: none"> <li>Added RED-DA (EN 13081) statement and supporting sections to Regulatory compliance information chapter.</li> </ul> | August 2025  |

| 1.8 | ADRASTEAL<br>I_06.006 | 1.0 | <ul style="list-style-type: none"> <li>Updated Application MCU information Application MCU, Introduction, Module Key Features chapters.</li> </ul>        | January 2026 |

## 2 Abbreviations

| Abbreviation     | Name                                                                        |

|------------------|-----------------------------------------------------------------------------|

| 3GPP             | 3rd Generation Partnership Project                                          |

| ADC              | Analog-to-Digital Converter                                                 |

| ASCI             | Advanced Speech Call Items                                                  |

| APN              | Access Point Name                                                           |

| BCD              | Binary Coded Decimal                                                        |

| CLK              | Clock signal                                                                |

| DH               | Deep Hibernation                                                            |

| eDRX             | Extended Discontinuous Reception                                            |

| EJTAG            | Embedded Joint Test Action Group                                            |

| GLONASS          | Global Navigation Satellite System                                          |

| GNSS             | Global Navigation Satellite System                                          |

| GPS              | Global Positioning System                                                   |

| GPIO             | General Purpose Input Output                                                |

| I <sup>2</sup> C | Inter-Integrated Circuit                                                    |

| IoT              | Internet of Things                                                          |

| IMEI             | International Mobile station Equipment Identity                             |

| IMEISV           | International Mobile station Equipment Identity and Software Version number |

| JTAG             | Joint Test Action Group                                                     |

| LTE              | Long Term Evolution                                                         |

| MCU              | Micro controller Unit                                                       |

| MISO             | Master In Slave Out                                                         |

| ME               | Mobile Equipment                                                            |

| MOSI             | Master Out Slave in                                                         |

| MT               | Mobile Termination                                                          |

| MTU              | Maximum Transfer Unit                                                       |

| PA               | Power Amplifier                                                             |

| PD               | Power Down                                                                  |

| PMU              | Power Management Unit                                                       |

| PSM              | Power Save Mode                                                             |

| RAM              | Random Access Memory                                                        |

| RAT              | Radio Access Technology                                                     |

| RLP              | Radio Link Protocol                                                         |

| RTC              | Real Time Clock                                                             |

|       |                                             |

|-------|---------------------------------------------|

| SINAD | Signal to Noise and Distortion ratio        |

| SIM   | Subscriber Identity Module                  |

| SPI   | Serial Peripheral Interface                 |

| SVN   | Software Version Number                     |

| TA    | Terminal Adaptor                            |

| TCXO  | Temperature Compensated Crystal Oscillator  |

| TE    | Terminal Equipment                          |

| TTFF  | Time To First Fix                           |

| UART  | Universal Asynchronous Receiver/Transmitter |

| UE    | User Equipment                              |

| UICC  | Universal Integrated Circuit Card           |

| USIM  | Universal Subscriber Identity Module        |

| XO    | Crystal Oscillator                          |

### 3 Introduction

Adrastea-I module is a compact LTE-M/NB-IoT Cellular module with integrated GNSS.

Based on the Sony Altair ALT1250 chipset, the Adrastea-I module provides AT-Command based multi-band configurability enabling international multi-regional coverage in LTE Cat M1 / NB1 radio access technologies.

Adrastea-I includes a fully integrated global navigation satellite system solution that supports GPS and GLONASS positioning systems.

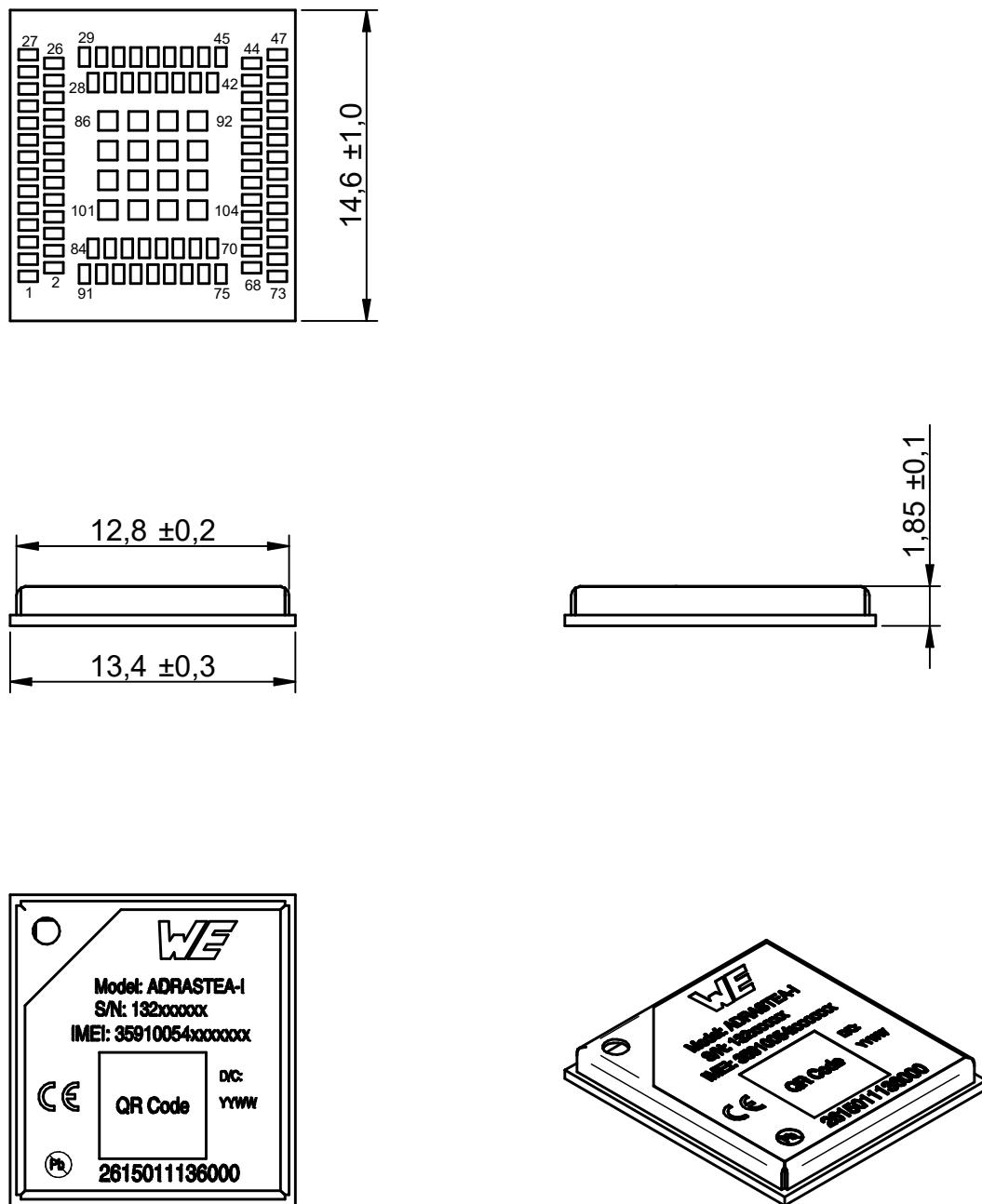

Compact 13.4mm x14.6mm x 1.85mm design allows the module to fit in small-size applications.

The module can be operated through one of two available cellular communication technologies:

- LTE-Cat.M or

- LTE-Cat.NB-IoT.

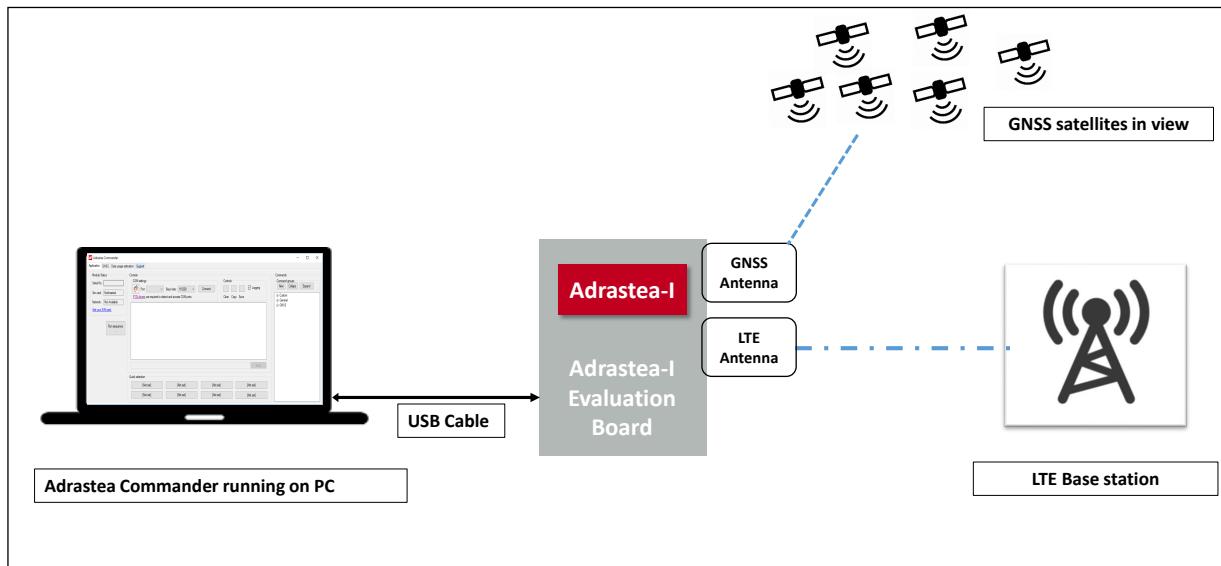

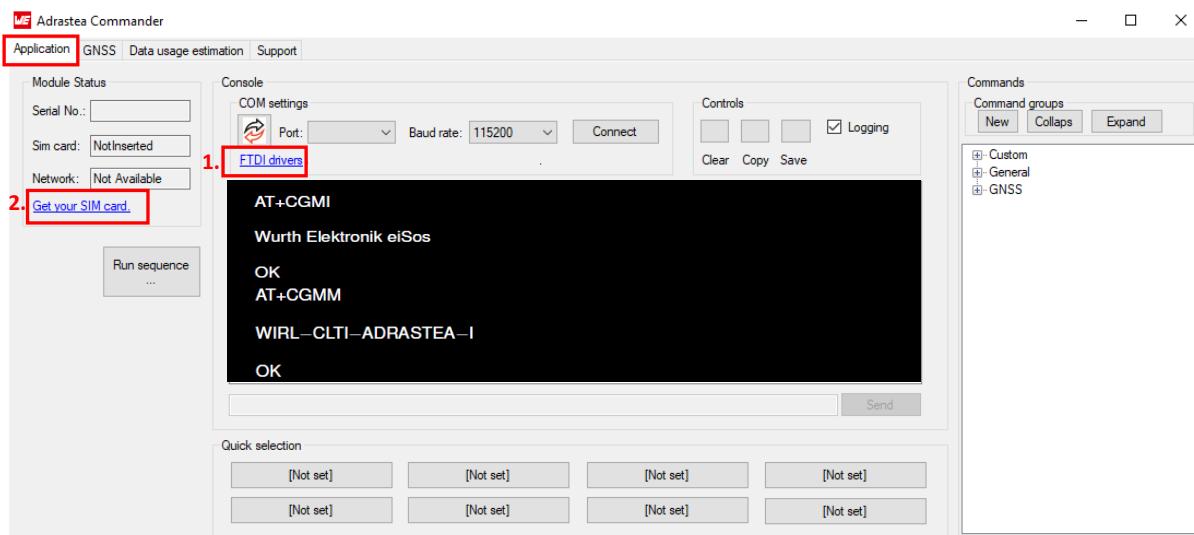

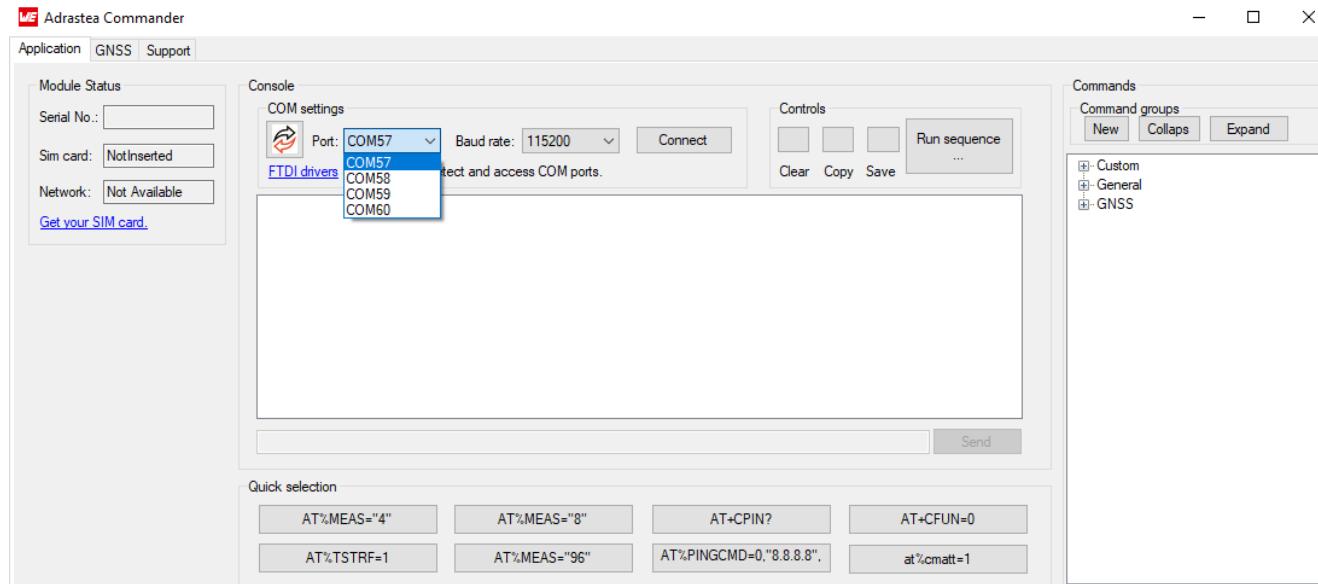

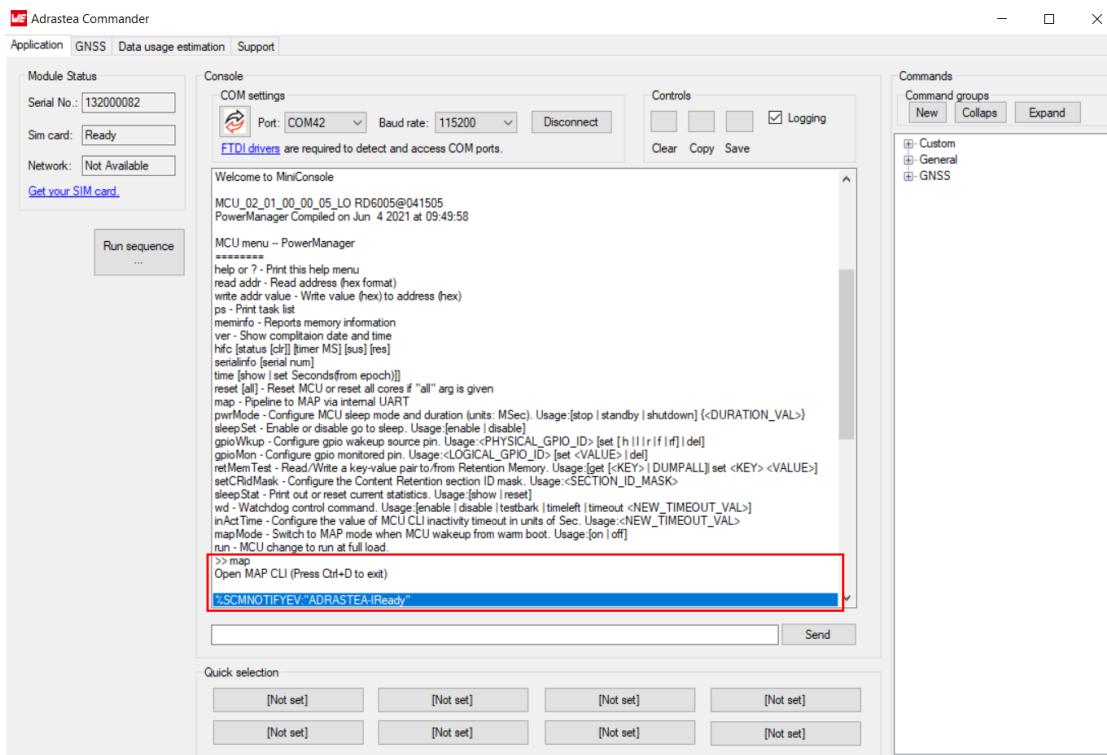

The Adrastea-I EV-Kit and "Adrastea Commander" tool ([1]) allow getting started with the module and testing its functionalities. The EV-Board can be connected to an USB port of a PC. The EV-Board also represents our reference design. For further information, Refer to the EV-Board manual [2].

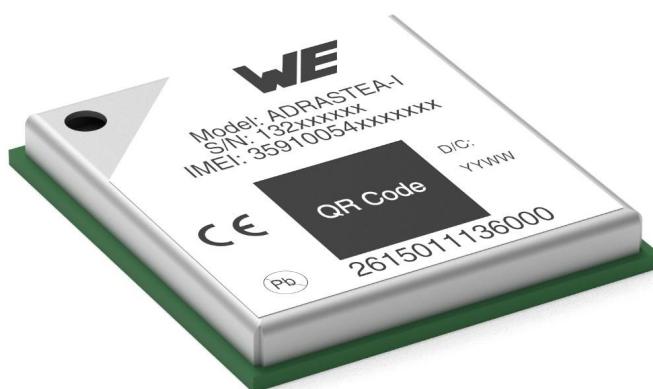

The module comes with the declaration of conformity (CE), is compliant to RoHS, REACH. The Adrastea-I module is GCF and Deutsche Telekom certified.

Figure 1: Adrastea-I

### 3.1 Adrastea-I GCF Certification

Adrastea-I is GCF certified module. Major advantage with GCF certified module integrated in end IoT application is that it reduces efforts for industry and operator specific certifications. However, customer shall check certification requirements with network operator before commercial deployment of IoT devices.

Figure 2: Adrastea-I GCF Certification

### 3.2 Adrastea-I Deutsche Telekom Certification

Adrastea-I is certified by Deutsche Telekom.

To Würth Elektronik

Forward to Ravindra Singh

From Miguel Rodriguez (Deutsche Telekom AG)

Contact E-Mail: [miguel.rodriguez@telekom.de](mailto:miguel.rodriguez@telekom.de)

Date 07<sup>th</sup> February, 2022

Subject Limited Certification for Würth Elektronik ADASTREA-I Communication Module

Dear Würth Elektronik Team,

Deutsche Telekom issues a limited certification for your ADASTREA-I communication module:

|                                          |                                                                             |

|------------------------------------------|-----------------------------------------------------------------------------|

| Concept Class                            | LPWA-enabled, multi-mode module (NB1, LTE-M)                                |

| Deutsche Telekom (DT) Certification Date | 07.02.2022                                                                  |

| DT Responsible Entity / Contact          | VTI-IOT / Miguel Rodriguez                                                  |

| Certified Deutsche Telekom Affiliates*   | (Limited) NB-IoT: AT, CZ, DE, HR, NL, PL, SK<br>(Limited) LTE-M: AT, DE, NL |

| OEM Firmware Version                     | ADRASTEA-I_06.006                                                           |

| OEM Hardware Version                     | V1.0                                                                        |

\* Please refer to the OEM Certification Report for Deutsche Telekom Affiliate Country Codes.

Detailed conditions for this limited certification are listed below. Until these topics are addressed, a full technical certification is not granted by Deutsche Telekom. For more details, please refer to the OEM Certification Report of this product.

- OEM is required to present GCF certification for this product.

Deutsche Telekom considers this product to be suitable for IoT projects having large volumes, as there is support for the no-harm to network / communication efficiency feature GSMA TS.34 Radio Policy Manager (RPM).

Kind regards,

Deutsche Telekom AG

Miguel Rodriguez

Digital

unterschrieben von

Miguel Rodriguez

Datum: 2022.02.07

15:10:05 +01'00'

Miguel Rodriguez

Sr. Mgr., IoT Device Verification & Engineering

Adrian Orlikowski

Mgr., IoT Device Verification & Engineering

Address Deutsche Telekom AG

Landgrabenweg 151, 53227 Bonn

Contact +49 228 181-0, E-Mail: [info@telekom.de](mailto:info@telekom.de)

Supervisory Board Timotheus Höttges (Chairman),

Board of Directors Adel Al-Saleh, Birgit Bohle, Srinivasan Gopalan, Dr. Christian P. Illek, Thorsten Langheim, Dominique Leroy, Claudia Nemat

Commercial register Amtsgericht Bonn HRB 6794

Registered office Bonn

VAT ID No. DE 123475223

WEEE Reg.-No. DE50478376

Figure 3: Adrastea-I Deutsche Telekom Certification

### 3.3 Benefits of Deutsche Telekom Certified Module

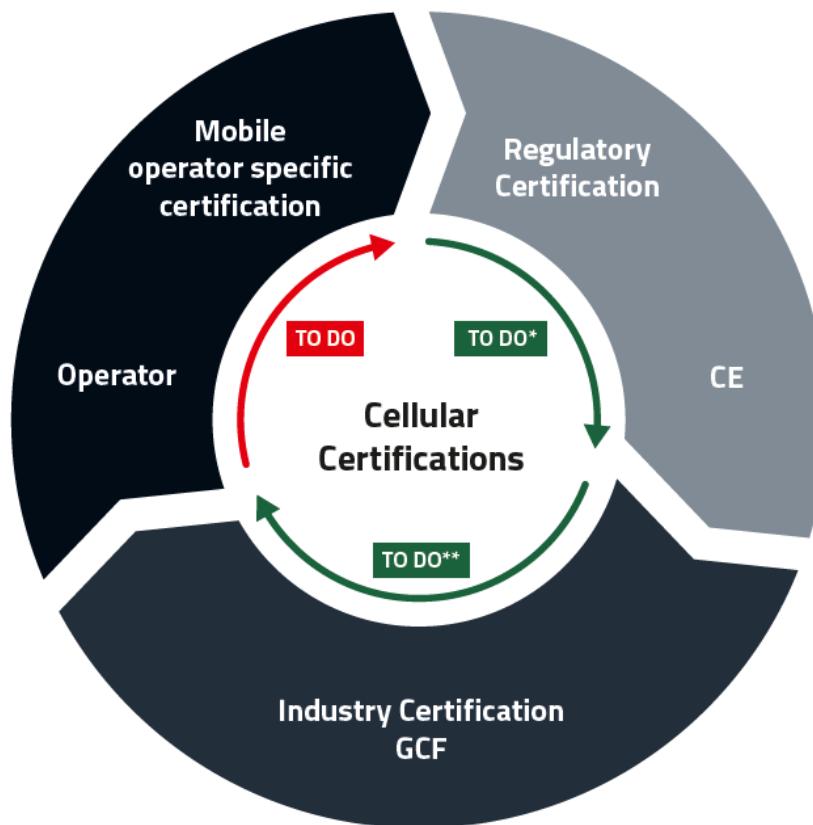

Normal Cellular Certification procedure includes 3 different types of certifications:

- Regulatory Certification: CE, FCC and similar based on region.

- Industry Specific Certification: GCF, PTCRB

- Network Operator Certification: Vodafone, Deutsche Telekom, AT&T etc.

\* To do on device level, Adrastea-I offers CE declaration

\*\* To do on device level, Adrastea-I offers GCF certification

Figure 4: Normal Cellular Certification Process

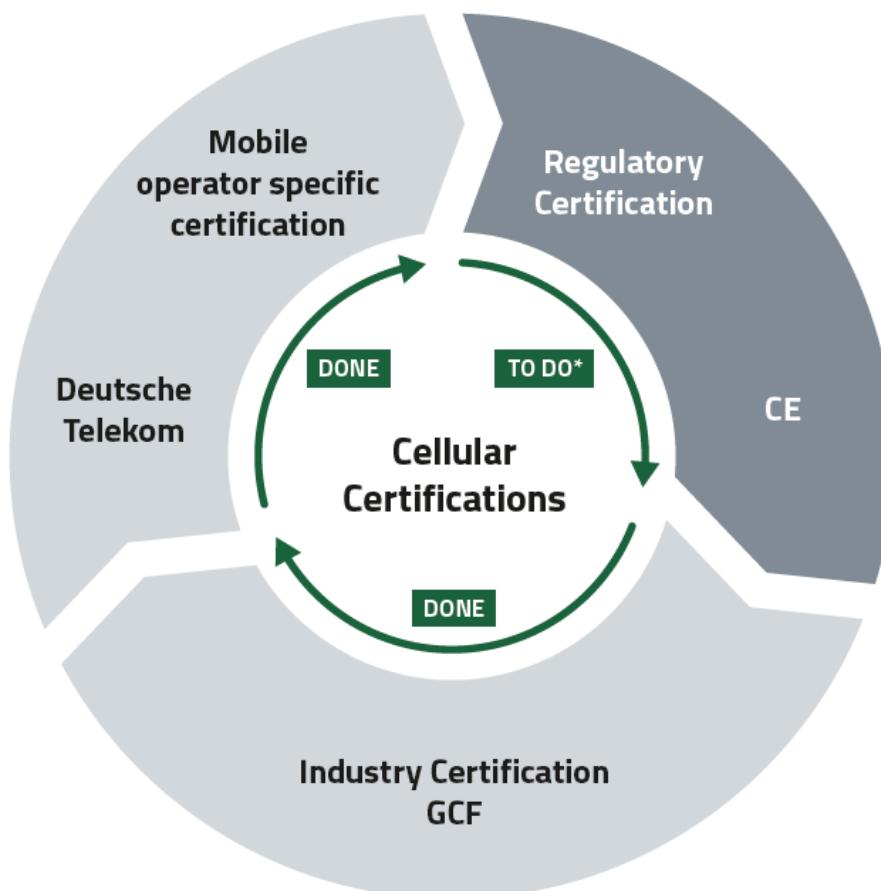

Pre-Certified Adrastea-I module from Deutsche Telekom brings the following key advantages:

- It enables integration to end device without further end device label Industry specific Certification (i.e. GCF) and Network Operator Certification (Deutsche Telekom).

Regulatory Certifications (i.e. CE, FCC and similar based on region) are still required for the end product.

- Obtain assurance: Pre-certified module reduces the final test effort.

- Save time and money: The end product does not require to go through complex cellular certification process again.

The benefits of certification are applicable exclusively when the customer utilizes connectivity (IoT SIM cards) provided by Deutsche Telekom. To obtain the certification benefits, the customer must use connectivity (IoT SIM cards) from Deutsche Telekom. It is required that the customer contacts Deutsche Telekom to acquire the necessary IoT SIM cards.

\*To do on device level, Adrastea-I offers CE declaration

Figure 5: Benefits of Deutsche Telekom Certified Module

### 3.4 Module Key Features

| Feature                  | Description                                                                                                                                                                                  |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Physical Dimensions      | 13.4mm x 14.6mm x 1.85mm                                                                                                                                                                     |

| Supported Networks       | <ul style="list-style-type: none"> <li>- LTE-Cat.M</li> <li>- LTE-Cat.NB-IoT</li> </ul>                                                                                                      |

| LTE Supported Bands      | <b>LTE-Cat.M:</b> B2/B3/B4/B5/B8/B12/B20/B25/B26/B28<br><b>LTE-Cat.NB-IoT:</b> B3/B5/B8/B20/B28                                                                                              |

| Module Interfaces        | <ul style="list-style-type: none"> <li>- USIM</li> <li>- UART</li> <li>- I<sup>2</sup>C Master</li> <li>- SPI Master</li> <li>- GPIO</li> <li>- ADC</li> <li>- JTAG</li> </ul>               |

| Integrated GNSS          | Adrastea-I includes a fully integrated global navigation satellite system solution that supports GPS and GLONASS positioning system.                                                         |

| Output Power class       | Power Class 3 (23 dBm)                                                                                                                                                                       |

| Maximum Data Rate        | <b>LTE-Cat.M:</b> Downlink: 300 Kbps, Uplink: 375 Kbps                                                                                                                                       |

|                          | <b>LTE-Cat.NB-IoT:</b> Downlink: 27.2 Kbps, Uplink: 62.5 Kbps                                                                                                                                |

| 3GPP Standard Compliance | 3GPP Release 13 compliant, Upgradable to Rel 14                                                                                                                                              |

| Firmware Upgrade         | <ul style="list-style-type: none"> <li>- Secure Firmware upgrade over UART</li> <li>- Secure Firmware upgrade over air</li> </ul>                                                            |

| Supported Protocols      | <ul style="list-style-type: none"> <li>- IPv4, IPv6</li> <li>- TCP/UDP SOCKET</li> <li>- HTTP/HTTPS</li> <li>- TLS/DTLS (TLS Version 1.2)</li> <li>- LWM2M Client</li> <li>- MQTT</li> </ul> |

| AT Commands              | 3GPP TS 27.007 and 3GPP TS 27.005 AT commands, as well as Würth Elektronik eiSos enhanced AT commands                                                                                        |

| Operating Voltage        | <ul style="list-style-type: none"> <li>- VDD: From 2.3 V to 4.3 V</li> <li>- VDD_FEM: From 3.1 V to 4.3 V</li> </ul>                                                                         |

| Temperature Range        | Operation temperature: -40 °C to +85 °C                                                                                                                                                      |

Table 3: Module Key Features

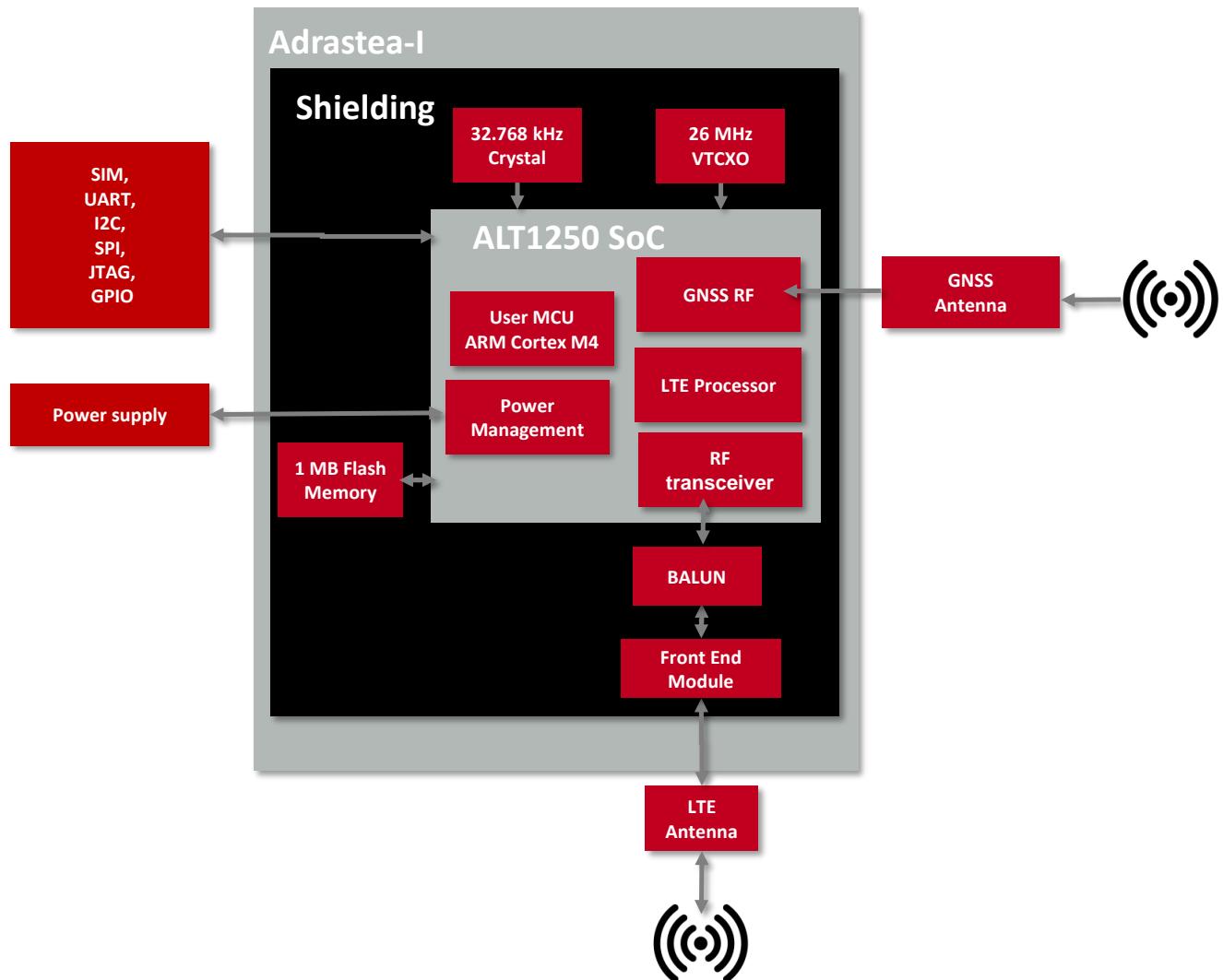

### 3.5 Block diagram

Figure 6: Block diagram

### 3.6 Ordering information

| WE order code | Description                                   |

|---------------|-----------------------------------------------|

| 2615011136000 | Cellular LTE-M/NB-IoT module in T&R packaging |

| 2615029236001 | Cellular LTE-M/NB-IoT EV-Kit                  |

Table 4: Ordering information

## 4 Electrical and Radio Specifications

Unless otherwise stated, all the values given in the manual were measured on the Adrastea-I EV-Board under the following conditions: T = 25 °C and powered via 5 V/1A Power Jack. The voltage regulator of the EV-Board regulates the connected voltage 5 V down to 3.6 V and supplies the remaining parts of the circuit. If the EV-Board is power sourced, the power LED1 lights up.

### 4.1 Operating Conditions

| Parameter                | Direction | Min. | Typ. | Max. | Unit |

|--------------------------|-----------|------|------|------|------|

| Supply voltage (VDD)     | Supply    | 2.3  | 3.6  | 4.3  | V    |

| Supply voltage (VDD_FEM) | Supply    | 3.1  | 3.6  | 4.3  | V    |

| VSIM                     | Output    | 1.7  | 1.8  | 1.9  | V    |

| VDDIO                    | Output    | 1.7  | 1.8  | 1.9  | V    |

| Operating temperature    |           | -40  | 25   | 85   | °C   |

Table 5: Operating conditions

### 4.2 Current Consumption

#### 4.2.1 LTE-Cat.M Mode

| Description       | Test Condition                            | Value | Unit |

|-------------------|-------------------------------------------|-------|------|

| LTE-IDLE          | MCU RUN                                   | 16.8  | mA   |

|                   | MCU SHUTDOWN                              | 2.9   | mA   |

| Peak Current (TX) | TX @23dBm, MCU RUN                        | 454.2 | mA   |

| PSM Current (DH0) | MCU SHUTDOWN, LTE RF Disabled (AT+CFUN=0) | 1.57  | µA   |

| PSM Current (DH1) | MCU SHUTDOWN, LTE RF Disabled (AT+CFUN=0) | 39.6  | µA   |

| PSM Current (DH2) | MCU SHUTDOWN, LTE RF Disabled (AT+CFUN=0) | 82.2  | µA   |

| GNSS-Active       | MCU RUN, LTE RF Disabled (AT+CFUN=0)      | 53.98 | mA   |

Table 6: LTE-Cat.M Current consumption

#### 4.2.2 LTE-Cat.NB-IoT Mode

| Description       | Test Condition                                  | Value | Unit |

|-------------------|-------------------------------------------------|-------|------|

| LTE-IDLE          | MCU RUN                                         | 15.7  | mA   |

|                   | MCU SHUTDOWN                                    | 2.8   | mA   |

| Peak Current (TX) | TX @23dBm, MCU RUN                              | 434   | mA   |

| PSM Current (DH0) | MCU SHUTDOWN, LTE<br>RF Disabled<br>(AT+CFUN=0) | 1.57  | µA   |

| PSM Current (DH1) | MCU SHUTDOWN, LTE<br>RF Disabled<br>(AT+CFUN=0) | 38.5  | µA   |

| PSM Current (DH2) | MCU SHUTDOWN, LTE<br>RF Disabled<br>(AT+CFUN=0) | 81.5  | µA   |

Table 7: NB-IoT Current consumption

### 4.3 LTE Radio Characteristics

Module performance is based on the quality of the RF link from LTE network to the Adrastea-I module.

The following factors and tasks are critical for the performance of the Adrastea-I module:

- External LTE antenna for signal reception from LTE network.

- RF trace delivering the signal from the external antenna to the LTE RF pad of the Adrastea-I module

- Minimization of external and environmental effects.

#### 4.3.1 LTE Supported Bands

#### 4.3.2 LTE-Cat.M Mode

| Band | Transmit Band (Tx) | Receive Band (Rx) | Unit |

|------|--------------------|-------------------|------|

| B2   | 1850 - 1910        | 1930 - 1990       | MHz  |

| B3   | 1710 - 1785        | 1805 - 1880       | MHz  |

| B4   | 1710 - 1755        | 2110 - 2155       | MHz  |

| B5   | 824 - 849          | 869 - 894         | MHz  |

| B8   | 880 - 915          | 925 - 960         | MHz  |

| B12  | 699 - 716          | 729 - 746         | MHz  |

| B20  | 832 - 862          | 791 - 821         | MHz  |

| B25  | 1850 - 1915        | 1930 - 1995       | MHz  |

| B26  | 814 - 849          | 859 - 894         | MHz  |

| B28  | 703 - 748          | 758 - 803         | MHz  |

Table 8: LTE-Cat.M Supported Bands

#### 4.3.3 LTE-Cat.NB-IoT Mode

| Band | Transmit Band (Tx) | Receive Band (Rx) | Unit |

|------|--------------------|-------------------|------|

| B3   | 1710 - 1785        | 1805 - 1880       | MHz  |

| B5   | 824 - 849          | 869 - 894         | MHz  |

| B8   | 880 - 915          | 925 - 960         | MHz  |

| B20  | 832 - 862          | 791 - 821         | MHz  |

| B28  | 703 - 748          | 758 - 803         | MHz  |

Table 9: LTE-Cat.NB-IoT Supported Bands

#### 4.3.4 RF Receiving Sensitivity

Unless noted otherwise, the Adrastea-I evaluation board is in static mode, values were measured with Rohde and Schwarz CMW500 equipment.

#### 4.3.5 LTE-Cat.M Reference sensitivity

| Band | Band Width | Value  | Unit |

|------|------------|--------|------|

| B2   | 1.4 MHz    | -105   | dBm  |

| B3   | 1.4 MHz    | -106.4 | dBm  |

| B4   | 1.4 MHz    | -106.2 | dBm  |

| B5   | 1.4 MHz    | -106.2 | dBm  |

| B8   | 1.4 MHz    | -107.2 | dBm  |

| B12  | 1.4 MHz    | -105.6 | dBm  |

| B20  | 1.4 MHz    | -106.4 | dBm  |

| B25  | 1.4 MHz    | -106.8 | dBm  |

| B26  | 1.4 MHz    | -106.4 | dBm  |

| B28  | 1.4 MHz    | -106   | dBm  |

Table 10: LTE-Cat.M RX Sensitivity

#### 4.3.6 LTE-Cat.NB-IoT Reference sensitivity

| Band | Value | Unit |

|------|-------|------|

| B3   | -110  | dBm  |

| B5   | -110  | dBm  |

| B8   | -110  | dBm  |

| B20  | -110  | dBm  |

| B28  | -110  | dBm  |

Table 11: LTE-Cat.NB-IoT RX Sensitivity

#### 4.3.7 Maximum Output Power

Unless noted otherwise, the Adrastea-I evaluation board is in static mode, values were measured with Rohde and Schwarz CMW500 equipment.

#### 4.3.8 LTE-Cat.M Maximum Output Power

| Band | Band Width | Value | Unit |

|------|------------|-------|------|

| B2   | 5 MHz      | 22.9  | dBm  |

| B3   | 5 MHz      | 21.5  | dBm  |

| B4   | 5 MHz      | 21.4  | dBm  |

| B5   | 5 MHz      | 21.7  | dBm  |

| B8   | 5 MHz      | 22.9  | dBm  |

| B12  | 5 MHz      | 21.4  | dBm  |

| B20  | 5 MHz      | 21.7  | dBm  |

| B25  | 5 MHz      | 23.0  | dBm  |

| B26  | 5 MHz      | 21.8  | dBm  |

| B28  | 5 MHz      | 21.9  | dBm  |

Table 12: LTE-Cat.M Maximum Output Power

#### 4.3.9 LTE-Cat.NB-IoT Maximum Output Power

| Band | Value | Unit |

|------|-------|------|

| B3   | 21.8  | dBm  |

| B5   | 22.0  | dBm  |

| B8   | 23.7  | dBm  |

| B20  | 22.1  | dBm  |

| B28  | 22.4  | dBm  |

Table 13: LTE-Cat.NB-IoT Maximum Output Power

## 4.4 GNSS Radio Characteristics

Module performance is based on the quality of the RF link from GNSS satellites to the module.

The following factors and tasks are critical for the performance of the integrated GNSS:

- Free/unimpacted line of sight

- External GNSS antenna for signal reception from GNSS satellites

- RF trace delivering the signal from the external antenna to the RF pad of the GNSS module

- Minimization of external and environmental effects

Adrastea-I supports GPS and GLONASS satellite systems using dedicated hardware accelerators in a power and cost efficient manner. The GNSS receiver shares certain hardware resources with the modem. This enables GNSS measurement slots to be efficiently scheduled based on the modem link state. The device key target is to allow GNSS positioning for asset management applications where infrequent position updates are required.

The Adrastea-I GNSS shares the RF Rx path with the LTE modem and, therefore, cannot operate in parallel with LTE data transfer. Hence this GNSS is not suitable for products that inherently require this co-existence, LTE connection and GNSS tracking.

GNSS cannot co-exist with LTE data transfer. LTE communication has higher priority over GNSS and, therefore, GNSS is automatically shut down once LTE is active (if it was active). While LTE is active, GNSS cannot be activated and all GNSS AT commands are responded with error.

### 4.4.1 GNSS Supported Constellation

Adrastea-I supports the following constellation (Satellite systems):

- GPS

- GLONASS

### 4.4.2 GNSS: Operating frequencies

| Description     | Min  | Typ. | Max  | Unit |

|-----------------|------|------|------|------|

| Input Frequency | 1560 |      | 1610 | MHz  |

Table 14: Radio characteristics

#### 4.4.3 GNSS: Rx Sensitivity

Module sensitivity is the weakest signal level the receiver can work with and it depends on the state of the module.

- Cold start sensitivity is the minimum power required by the module to acquire satellites and perform first fix in cold start.

- Hot start sensitivity is the minimum power required by the module to acquire satellites and perform first fix in hot start.

- Tracking sensitivity is the minimum power required by the module to keep in track of the position fix.

| Parameter  | Test Condition | Value | Unit |

|------------|----------------|-------|------|

| Cold Start | GPS-GLONASS    | -145  | dBm  |

| Hot Start  | GPS-GLONASS    | -152  | dBm  |

| Tracking   | GPS-GLONASS    | -160  | dBm  |

Table 15: GNSS RX Sensitivity

#### 4.4.4 GNSS: Time To First Fix

The Time To First Fix (TTFF) is the time needed by the module to achieve the first valid position fix, once the module is powered up or returns from a period of signal blockage.

GNSS update rate for Adrastea-I is 1 Hz (once per second).

Depending on the type of start (cold or hot), a different TTFF performance is given below.

| Parameter  | Test Condition                     | Value | Unit |

|------------|------------------------------------|-------|------|

| Cold Start | GPS-GLONASS, Power Level = -120dBm | 36    | s    |

| Hot Start  | GPS-GLONASS, Power Level = -120dBm | 1     | s    |

Table 16: GNSS Time to First Fix

#### 4.4.5 GNSS: Position Accuracy

| Parameter         | Test Condition                           | Value | Unit |

|-------------------|------------------------------------------|-------|------|

| Position Accuracy | GPS-GLONASS,<br>Power Level =<br>-120dBm | 1.5   | m    |

Table 17: GNSS Position Accuracy

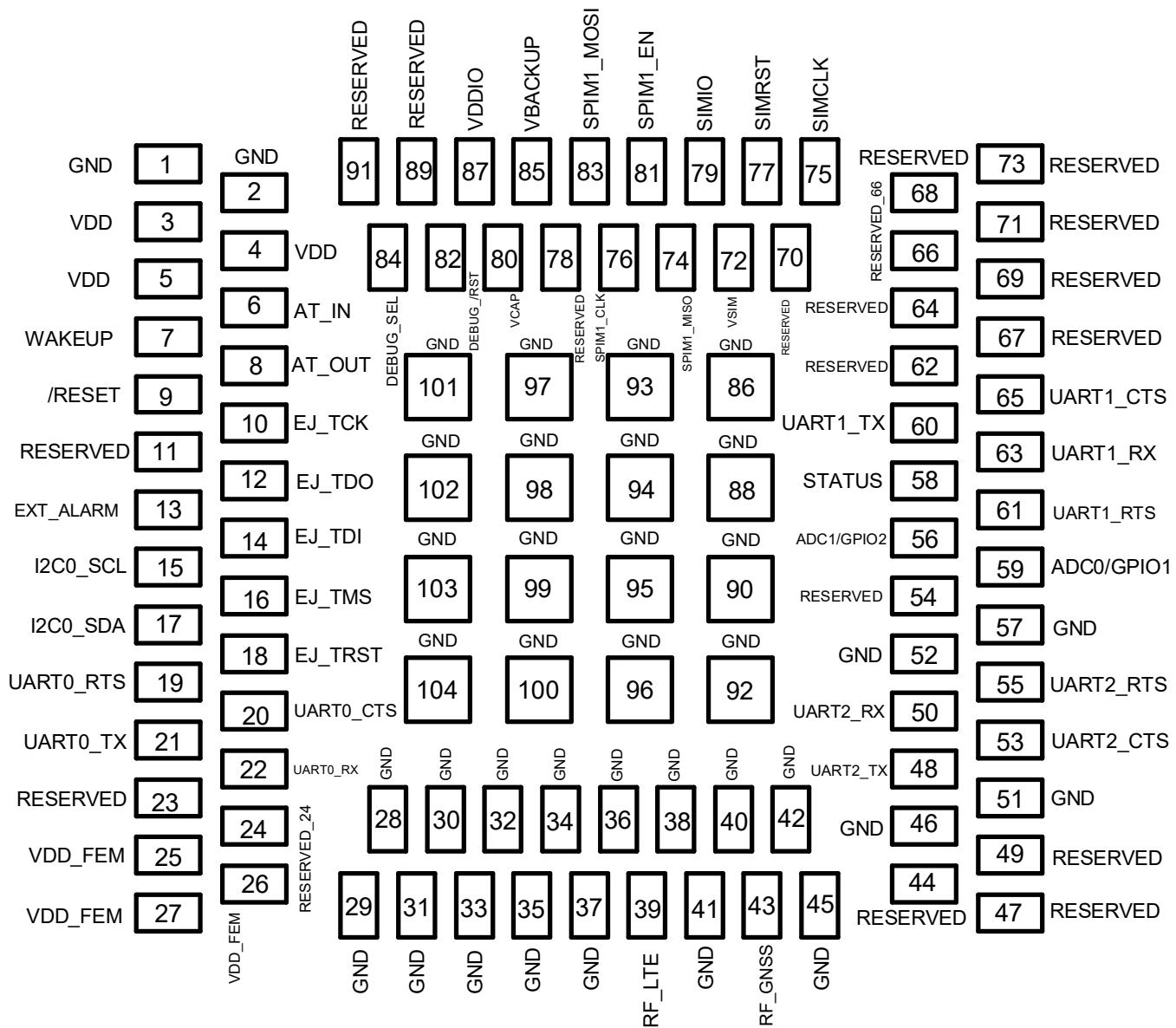

## 5 Pinout

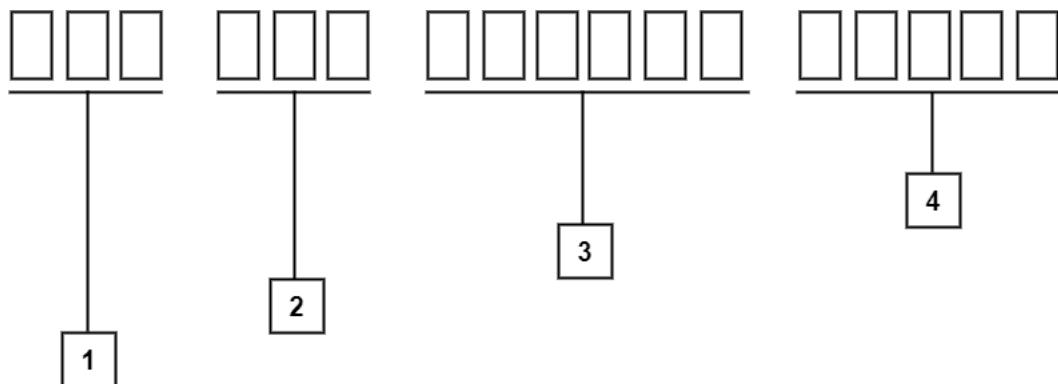

Figure 7: Pinout (top view)

| Pin Number | Designation      | I/O          | Description                                                                                                                                            |

|------------|------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | <i>GND</i>       | Supply       | Negative Supply Voltage                                                                                                                                |

| 2          | <i>GND</i>       | Supply       | Negative Supply Voltage                                                                                                                                |

| 3          | <i>VDD</i>       | Supply       | Power supply for module                                                                                                                                |

| 4          | <i>VDD</i>       | Supply       | Power supply for module                                                                                                                                |

| 5          | <i>VDD</i>       | Supply       | Power supply for module                                                                                                                                |

| 6          | <i>AT_IN</i>     | Input        | Anti-tamper input                                                                                                                                      |

| 7          | <i>WAKEUP</i>    | Input        | Wakeup active high<br>Default pull resistor at power up and after DH0: No pull<br>DH2 state: No pull<br>DH1 state: No pull<br>DH0 state: No pull       |

| 8          | <i>AT_OUT</i>    | Output       | Anti-tamper output                                                                                                                                     |

| 9          | <i>/RESET</i>    | Input        | Reset active low                                                                                                                                       |

| 10         | <i>EJ_TCK</i>    | Input        | JTAG Test Clock                                                                                                                                        |

| 11         | <i>RESERVED</i>  | —            | Reserved (Shall be soldered but not connected.)                                                                                                        |

| 12         | <i>EJ_TDO</i>    | Output       | JTAG Test Data Output                                                                                                                                  |

| 13         | <i>EXT_ALARM</i> | Output       | Alarm Output                                                                                                                                           |

| 14         | <i>EJ_TDI</i>    | Input        | JTAG Test Data Input                                                                                                                                   |

| 15         | <i>I2C0_SCL</i>  | Input/Output | I2C serial clock<br>Default pull resistor at power up and after DH0: Pull Up<br>DH2 state: SW configurable<br>DH1 state: No pull<br>DH0 state: No pull |

| 16         | <i>EJ_TMS</i>    | Input        | JTAG Test Mode Select                                                                                                                                  |

| 17         | <i>I2C0_SDA</i>  | Input/Output | I2C serial data<br>Default pull resistor at power up and after DH0: Pull Up<br>DH2 state: SW configurable<br>DH1 state: No pull<br>DH0 state: No pull  |

| 18         | <i>EJ_TRST</i>   | Input        | JTAG Test Reset (required external pull down)                                                                                                          |

|    |                  |        |                                                                                                                                                                     |

|----|------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 19 | <i>UART0_RTS</i> | Output | MCU UART0 Request to Send<br><br>Default pull resistor at power up and after DH0: Pull Up<br>DH2 state: SW configurable<br>DH1 state: No pull<br>DH0 state: No pull |

| 20 | <i>UART0_CTS</i> | Input  | MCU UART0 Clear to Send<br><br>Default pull resistor at power up and after DH0: Pull Up<br>DH2 state: SW configurable<br>DH1 state: No pull<br>DH0 state: No pull   |

| 21 | <i>UART0_TX</i>  | Output | MCU UART0 Transmit Data<br><br>Default pull resistor at power up and after DH0: Pull Up<br>DH2 state: SW configurable<br>DH1 state: No pull<br>DH0 state: No pull   |

| 22 | <i>UART0_RX</i>  | Input  | MCU UART0 Receive Data<br><br>Default pull resistor at power up and after DH0: Pull Up<br>DH2 state: SW configurable<br>DH1 state: No pull<br>DH0 state: No pull    |

| 23 | <i>RESERVED</i>  | —      | Reserved (Shall be soldered but not connected.)                                                                                                                     |

| 24 | <i>RESERVED</i>  | —      | Reserved (Shall be soldered but not connected.)                                                                                                                     |

| 25 | <i>VDD_FEM</i>   | Supply | Power supply for FEM (Front End Module)                                                                                                                             |

| 26 | <i>VDD_FEM</i>   | Supply | Power supply for FEM (Front End Module)                                                                                                                             |

| 27 | <i>VDD_FEM</i>   | Supply | Power supply for FEM (Front End Module)                                                                                                                             |

| 28 | <i>GND</i>       | Supply | Negative supply voltage                                                                                                                                             |

| 29 | <i>GND</i>       | Supply | Negative supply voltage                                                                                                                                             |

|    |            |              |                                                                                                                                                                                                                 |

|----|------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 30 | GND        | Supply       | Negative supply voltage                                                                                                                                                                                         |

| 31 | GND        | Supply       | Negative supply voltage                                                                                                                                                                                         |

| 32 | GND        | Supply       | Negative supply voltage                                                                                                                                                                                         |

| 33 | GND        | Supply       | Negative supply voltage                                                                                                                                                                                         |

| 34 | GND        | Supply       | Negative supply voltage                                                                                                                                                                                         |

| 35 | GND        | Supply       | Negative supply voltage                                                                                                                                                                                         |

| 36 | GND        | Supply       | Negative supply voltage                                                                                                                                                                                         |

| 37 | GND        | Supply       | Negative supply voltage                                                                                                                                                                                         |

| 38 | GND        | Supply       | Negative supply voltage                                                                                                                                                                                         |

| 39 | RF_LTE     | RF           | RF Signal LTE                                                                                                                                                                                                   |

| 40 | GND        | Supply       | Negative supply voltage                                                                                                                                                                                         |

| 41 | GND        | Supply       | Negative supply voltage                                                                                                                                                                                         |

| 42 | GND        | Supply       | Negative supply voltage                                                                                                                                                                                         |

| 43 | RF_GNSS    | RF           | RF Signal GNSS                                                                                                                                                                                                  |

| 44 | RESERVED   | —            | Reserved (Shall be soldered but not connected.)                                                                                                                                                                 |

| 45 | GND        | Supply       | Negative supply voltage                                                                                                                                                                                         |

| 46 | GND        | Supply       | Negative supply voltage                                                                                                                                                                                         |

| 47 | RESERVED   | —            | Reserved (Shall be soldered but not connected.)                                                                                                                                                                 |

| 48 | UART2_TX   | Output       | UART2 Transmit Data (CLI port)                                                                                                                                                                                  |

| 49 | RESERVED   | —            | Reserved (Shall be soldered but not connected.)                                                                                                                                                                 |

| 50 | UART2_RX   | Input        | UART2 Receive Data (CLI port)                                                                                                                                                                                   |

| 51 | GND        | Supply       | Negative supply voltage                                                                                                                                                                                         |

| 52 | GND        | Supply       | Negative supply voltage                                                                                                                                                                                         |

| 53 | UART2_CTS  | Input        | UART2 Clear to Send (CLI port)                                                                                                                                                                                  |

| 54 | RESERVED   | —            | Reserved (Shall be soldered but not connected.)                                                                                                                                                                 |

| 55 | UART2_RTS  | Output       | UART2 Request to Send (CLI port)                                                                                                                                                                                |

| 56 | ADC1/GPIO2 | Input/Output | Auxiliary Analog to Digital Converter<br>Input/Programmable GPIO<br><br>Default pull resistor at power up and<br>after DH0: Pull Down<br>DH2 state: SW configurable<br>DH1 state: No pull<br>DH0 state: No pull |

|    |            |              |                                                                                                                                                                                                          |

|----|------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 57 | GND        | Supply       | Negative supply voltage                                                                                                                                                                                  |

| 58 | STATUS     | Output       | Module Status                                                                                                                                                                                            |

| 59 | ADC0/GPIO1 | Input/Output | Auxiliary Analog to Digital Converter Input /Programmable GPIO<br><br>Default pull resistor at power up and after DH0: Pull Up<br>DH2 state: SW configurable<br>DH1 state: No pull<br>DH0 state: No pull |

| 60 | UART1_TX   | Output       | UART1 Transmit Data (Modem Log port)                                                                                                                                                                     |

| 61 | UART1_RTS  | Output       | UART1 Request to Send (Modem Log port)                                                                                                                                                                   |

| 62 | RESERVED   | —            | Reserved                                                                                                                                                                                                 |

| 63 | UART1_RX   | Input        | UART1 Receive Data (Modem Log port)                                                                                                                                                                      |

| 64 | RESERVED   | —            | Reserved (Shall be soldered but not connected.)                                                                                                                                                          |

| 65 | UART1_CTS  | Input        | UART1 Clear to Send (Modem Log port)                                                                                                                                                                     |

| 66 | RESERVED   | —            | Reserved (Shall be soldered but not connected.)                                                                                                                                                          |

| 67 | RESERVED   | —            | Reserved (Shall be soldered but not connected.)                                                                                                                                                          |

| 68 | RESERVED   | —            | Reserved (Shall be soldered but not connected.)                                                                                                                                                          |

| 69 | RESERVED   | —            | Reserved (Shall be soldered but not connected.)                                                                                                                                                          |

| 70 | RESERVED   | —            | Reserved (Shall be soldered but not connected.)                                                                                                                                                          |

| 71 | RESERVED   | —            | Reserved (Shall be soldered but not connected.)                                                                                                                                                          |

| 72 | VSIM       | Output       | SIM Output voltage                                                                                                                                                                                       |

| 73 | RESERVED   | —            | Reserved (Shall be soldered but not connected.)                                                                                                                                                          |

|    |                              |              |                                                                                                                                                                              |

|----|------------------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 74 | <i>SPIM1_MISO/</i><br>GPIO39 | Input/Output | MCU_SPIM1_MISO/Programmable GPIO<br><br>Default pull resistor at power up and after DH0: Pull Down<br>DH2 state: SW configurable<br>DH1 state: No pull<br>DH0 state: No pull |

| 75 | <i>SIMCLK</i>                | Output       | SIM Clock                                                                                                                                                                    |

| 76 | <i>SPIM1_CLK/</i><br>GPIO41  | Input/Output | MCU_SPIM1_CLK/Programmable GPIO<br><br>Default pull resistor at power up and after DH0: Pull Down<br>DH2 state: SW configurable<br>DH1 state: No pull<br>DH0 state: No pull  |

| 77 | <i>SIMRST</i>                | Output       | SIM Reset                                                                                                                                                                    |

| 78 | <i>RESERVED</i>              | —            | Reserved (Shall be soldered but not connected.)                                                                                                                              |

| 79 | <i>SIMIO</i>                 | Input/Output | SIM Data                                                                                                                                                                     |

| 80 | <i>VCAP</i>                  | Input/Output | Connecting external capacitor as backup for VDD                                                                                                                              |

| 81 | <i>SPIM1_EN/</i><br>GPIO40   | Input/Output | MCU SPI Enable/Programmable GPIO<br><br>Default pull resistor at power up and after DH0: Pull Up<br>DH2 state: SW configurable<br>DH1 state: No pull<br>DH0 state: No pull   |

| 82 | <i>DEBUG_RST</i>             | Input/Output | Reset pin for the JTAG probe                                                                                                                                                 |

| 83 | <i>SPIM1_MOSI/</i><br>GPIO38 | Input/Output | MCU_SPIM1_MOSI/Programmable GPIO<br><br>Default pull resistor at power up and after DH0: Pull Down<br>DH2 state: SW configurable<br>DH1 state: No pull<br>DH0 state: No pull |

|     |           |        |                                                             |

|-----|-----------|--------|-------------------------------------------------------------|

| 84  | DEBUG_SEL | Input  | Reset pin for the JTAG probe                                |

| 85  | VBACKUP   | Input  | Input from backup battery                                   |

| 86  | GND       | Supply | Negative supply voltage                                     |

| 87  | VDDIO     | Output | Output Voltage (it will turn off at DH0 and DH1 sleep mode) |

| 88  | GND       | Supply | Negative supply voltage                                     |

| 89  | RESERVED  | —      | Reserved (Shall be soldered but not connected.)             |

| 90  | GND       | Supply | Negative supply voltage                                     |

| 91  | RESERVED  | —      | Reserved(Shall be soldered but not connected.)              |

| 92  | GND       | Supply | Negative supply voltage                                     |

| 93  | GND       | Supply | Negative supply voltage                                     |

| 94  | GND       | Supply | Negative supply voltage                                     |

| 95  | GND       | Supply | Negative supply voltage                                     |

| 96  | GND       | Supply | Negative supply voltage                                     |

| 97  | GND       | Supply | Negative supply voltage                                     |

| 98  | GND       | Supply | Negative supply voltage                                     |

| 99  | GND       | Supply | Negative supply voltage                                     |

| 100 | GND       | Supply | Negative supply voltage                                     |

| 101 | GND       | Supply | Negative supply voltage                                     |

| 102 | GND       | Supply | Negative supply voltage                                     |

| 103 | GND       | Supply | Negative supply voltage                                     |

| 104 | GND       | Supply | Negative supply voltage                                     |

Table 18: Pinout

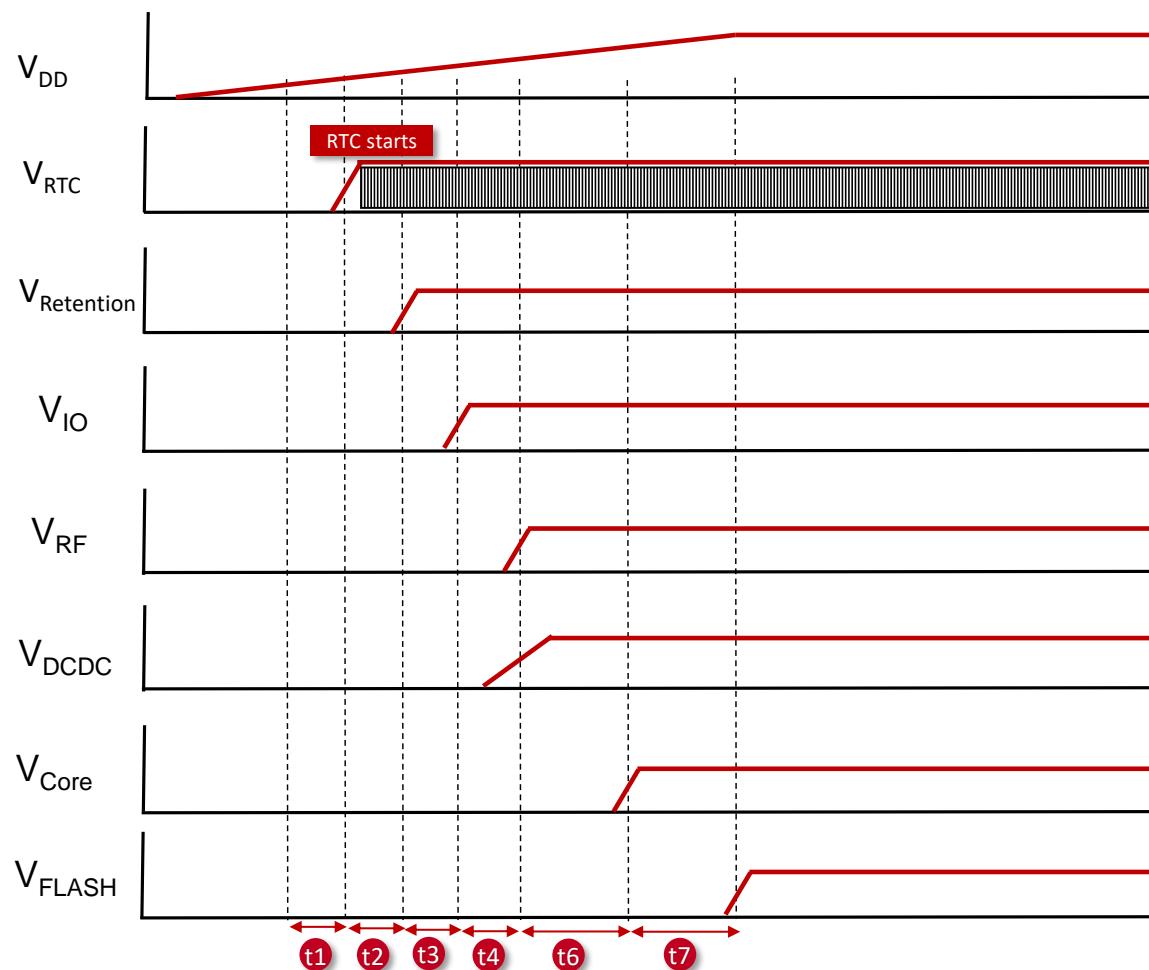

## 5.1 Module Power Up

An automatic power up sequence occurs when connecting the device to the power supply (VDD). The automatic power up sequence consists of the following phases:

- Phase 0: RET LDO to ramp up for supplying 1.0V retention core domain.

- Phase 1: I/O LDO to ramp up for supplying 1.8 V I/O domain.

- Phase 2: RF LDO to ramp up for supplying 1.9V RF domain.

- Phase 3: DCDC to ramp up for supplying 1.3V of Digital LDO and RF.

- Phase 4: DIG LDO to ramp up for supplying 1.0V of digital core domain.

- Phase 5: FLASH LDO to ramp up for supplying 1.8 V of Flash Domain.

Regulators will start ramping only with 1us delay from power good indication of previous phase. The automatic power up sequencing is shown below:

Figure 8: Adrastea-I Power up Sequence

| Parameter | Description                                                                                          | Min. | Max. | Unit |

|-----------|------------------------------------------------------------------------------------------------------|------|------|------|

| t1        | When VDD crosses the 0.8V threshold-VRTC should follow the VDD unless it has some capacitance on it. | 0    | 5    | μs   |

| t2        | Digital retention power up, the VDD slew rate has impact on this timing.                             | 70   | 100  | μs   |

| t3        | I/O LDO power up.                                                                                    | 10   | 60   | μs   |

| t4        | RF LDO power up.                                                                                     | 10   | 60   | μs   |

| t5        | DCDC boot time.                                                                                      | 100  | 200  | μs   |

| t6        | Core LDO power-up.                                                                                   | 10   | 60   | μs   |

| t7        | FLASH LDO power-up.                                                                                  | 10   | 60   | μs   |

Table 19: Power Up timing

## 5.2 Module Power Down

Power down sequence of the regulators will occur in following conditions:

- Turn off VDD.

- Shutdown is requested by */RESET* pin pulled to low.

## 5.3 Module Reset

Module reset will occur in following conditions:

- Perform power cycle - Turn off/on VDD and power up the device from reset state.

- Using */RESET* pin user can initiate power cycle that resets the device.

## 5.4 WAKEUP pin

This pin can be used to immediately wake up the module when being in low power state. This pin allows the module to get out of sleep mode when pulled HIGH.

The host connected to this pin should always keep the state of this pin (HIGH/LOW) at a known state (not floating) according to the required functionality.

- Pulled HIGH: Wake up internal MCU of module from sleep mode.

- Pulled LOW: Allowing internal MCU of module to go into sleep mode.

## 5.5 AT\_IN and AT\_OUT pins

User can connect the AT\_OUT pin to the AT\_IN pin in order to protect a device or module from tampering. The device will generate a software indication if the AT\_OUT and AT\_IN pins are disconnected.

The anti-tampering mechanism works in all active modes and all DHx power saving modes. If the anti-tampering is not in use, the AT\_IN should be shorted to GND.

## 5.6 /RESET pin

This pin has the highest priority compared to other chip functionalities, therefore asserting it will always force a hard reset. This pin is with internal PU resistor to 1.8V.

- Pulled HIGH: Turn on module regulators and power up the module.

- Pulled LOW: Turn off module regulators and shutdown the module.

- LOW to HIGH: Reset module (keep holding for at least 100 ms on LOW level before changing to HIGH).

## 5.7 EXT\_ALARM pin

The EXT\_ALARM pin can be used as an alarm indicator to an external host as per the Adrastea-I power mode. The behavior is as below:

| Module State | Test Condition             | EXT_ALARM Pin<br>Expected behavior |

|--------------|----------------------------|------------------------------------|

| DH0          | MCU Shutdown,<br>AT+CFUN=0 | High Impedance                     |

| DH1          | MCU Shutdown,<br>AT+CFUN=0 | High Impedance                     |

| DH2          | MCU Shutdown,<br>AT+CFUN=0 | LOW signal                         |

| Active       | MCU RUN                    | HIGH signal                        |

Table 20: EXT\_ALARM Pin

## 5.8 RF\_LTE pin

This is the LTE antenna pin. The impedance should be close to  $50 \Omega$ , VSWR (Voltage Standing Wave Ratio)  $< 1.5$ .

Connect  $50 \Omega$  transmission lines from this pin to the  $50 \Omega$  Primary Antenna/Antenna-connector. Refer to our hardware layout recommendations (chapter 9).

## 5.9 RF\_GNSS pin

This is the GNSS antenna pin. The impedance should be close to  $50 \Omega$ , VSWR (Voltage Standing Wave Ratio)  $< 1.5$ .

Connect  $50 \Omega$  transmission lines from this pin to the  $50 \Omega$  Primary Antenna/Antenna-connector. Refer to our hardware layout recommendations (chapter 9).

## 5.10 VBACKUP and VCAP pins

Adrastea-I supports a battery backup mechanism which allows seamless replacement of a weak battery. The battery should be replaced after the device is placed in DH0 state, and only when the RTC circuitry is operational, and is applied by VRTC.

The VBACKUP pin (battery) or the VCAP (capacitor) can be used as a backup during replacement. The VCAP pin should be left floating if a battery backup is used, while the VBACKUP pin should be left floating if a capacitor backup is used. If the application does not require a battery then both the VBACKUP and the VCAP pins should be left floating.

### 5.10.1 VCAP pin

The capacitor value should be large enough to keep the VCAP supply voltage above 1.8 V for as long as it takes for the battery to be replaced. Equation 1 should be used for calculating the capacitor value ( $C_{CAP}$ ).

Equation1:

$$C_{CAP} = (I_{CAP} \times T) / (V_{to} - V_{MIN})$$

The following parameters should be taken into account when making these calculations:

- The maximum current drawn from VCAP ( $I_{CAP} = 10\mu A$ ).

- The maximum period of time (T) it should take for battery replacement.

- The voltage that the capacitor was charged to ( $V_{to}$ ).

- The minimum voltage that the capacitor can discharge while still providing sufficient operational voltage for the RTC ( $V_{MIN} = 1.8$  V).

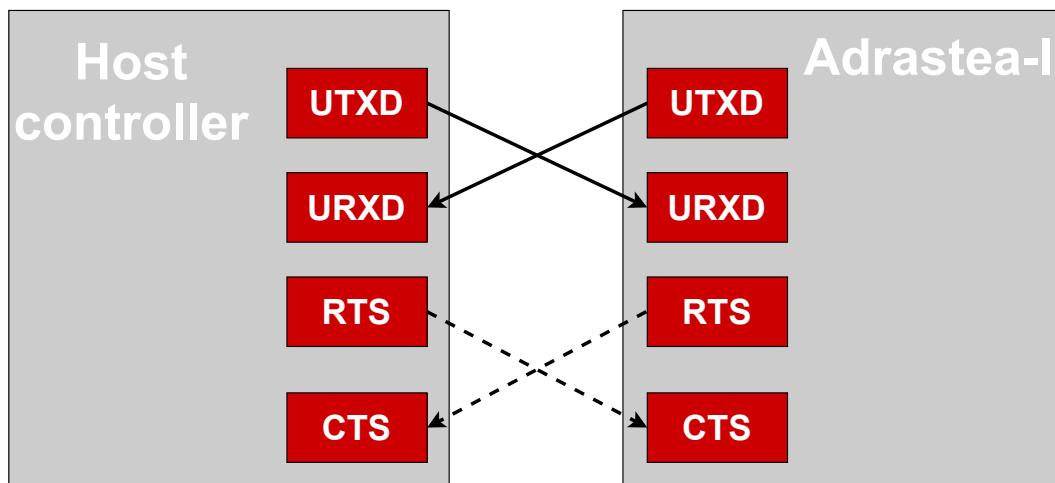

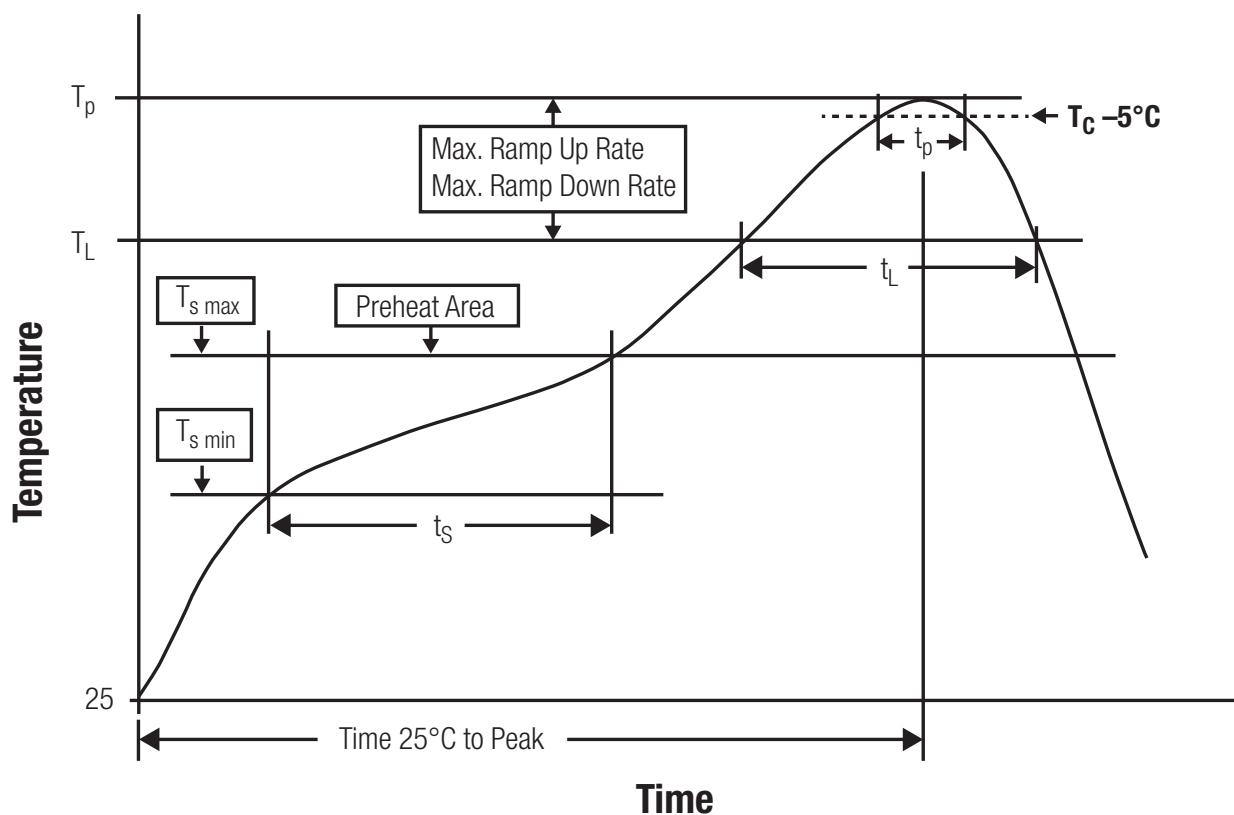

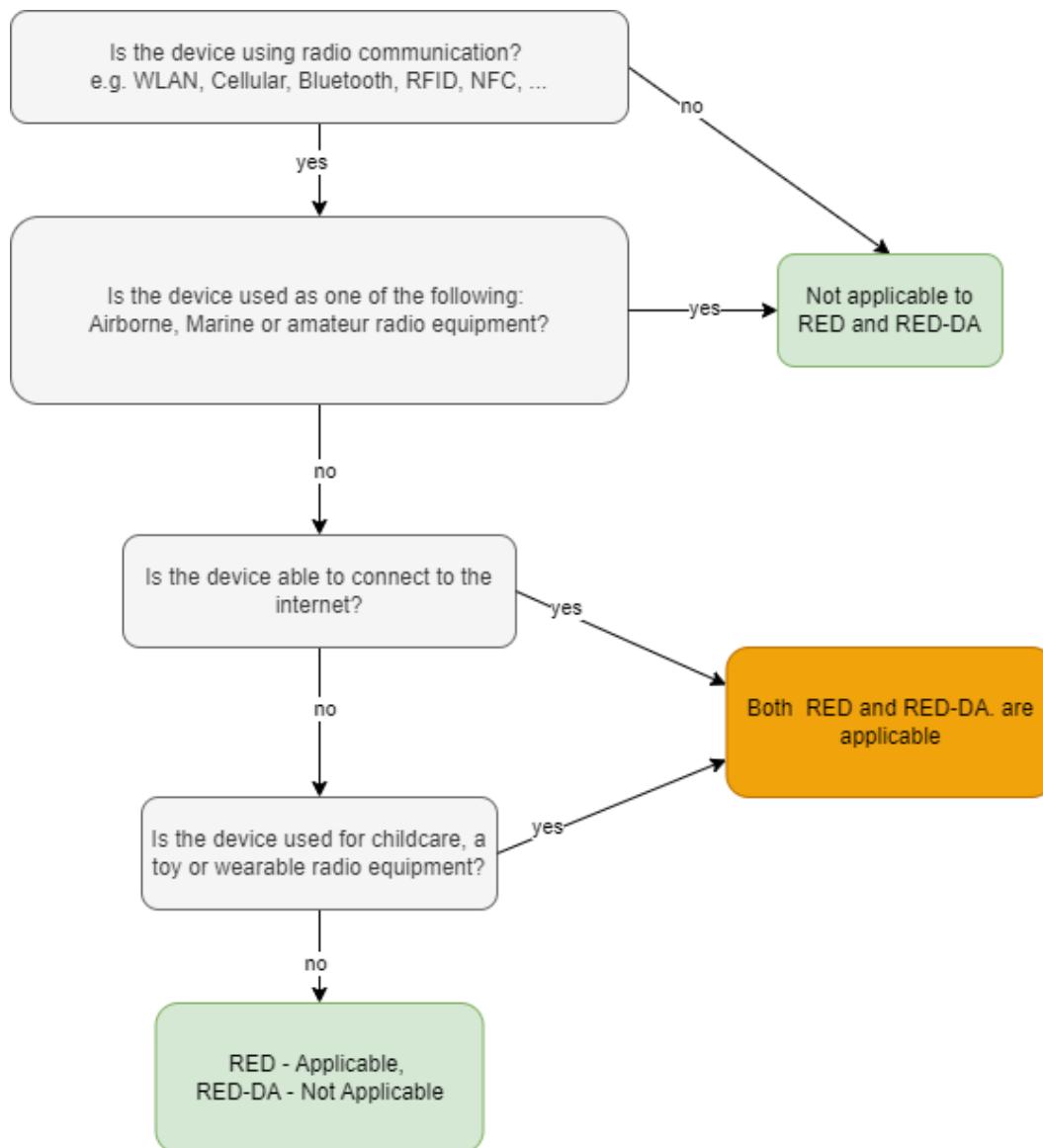

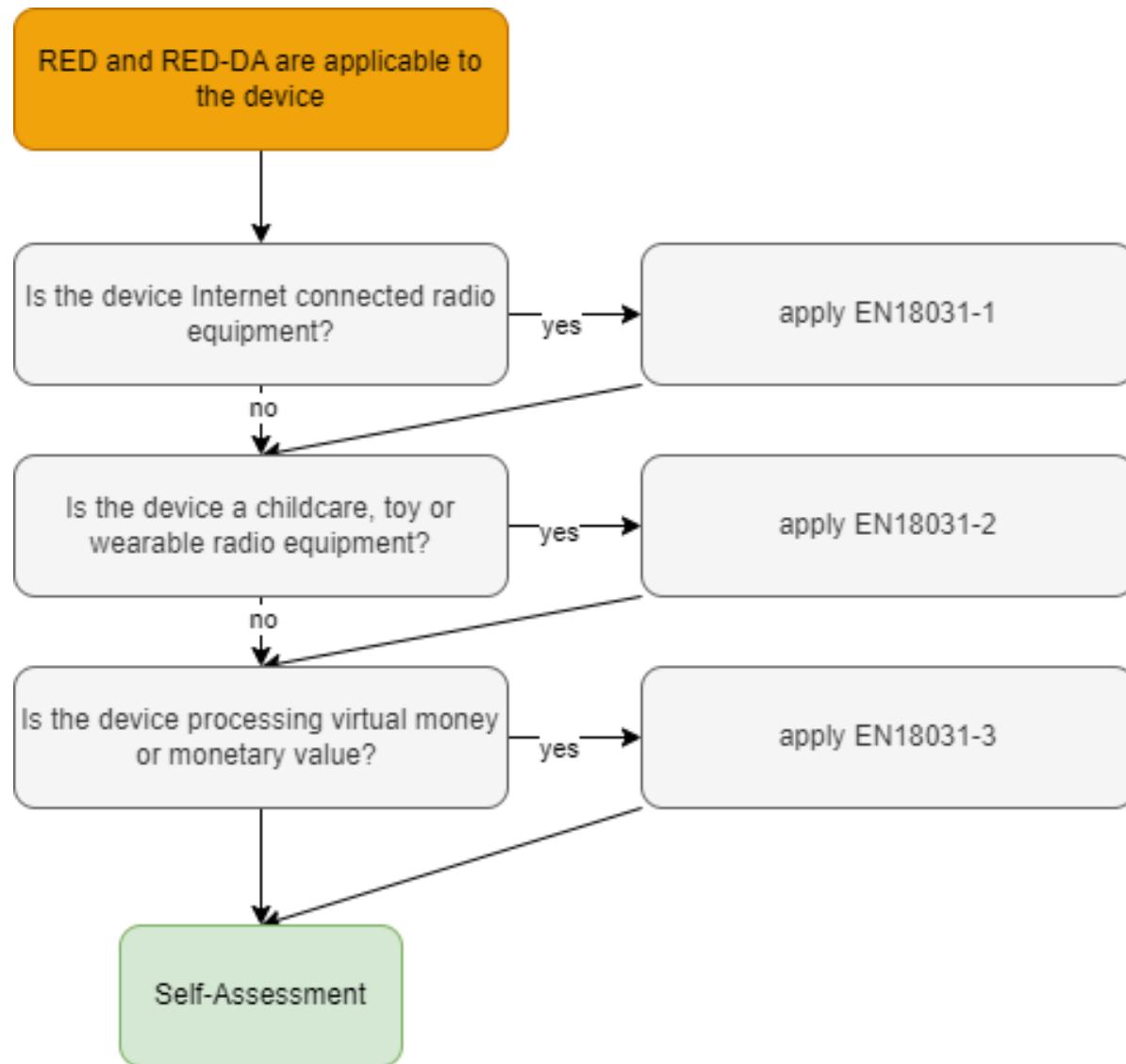

Example: